TFP401A原理图

请教大家,

谁有TFP401A的参考电路设计或者原理图能发我一份吗?我的邮箱是:leon.zhang.world@outlook.com

TI官网有没,哪里能找到呢?

非常感谢!

你好,给你发了一份简单参考,请注意查收

您好!可否同样发我一份,我的邮箱为nkuxiang@163.com,谢谢!

已发送,请注意查收

我也要一份,谢谢

liusum12@sina.com

我也需要一份,请发邮箱chengxg@nsechina.com

另外有个问题想求助一下您:

DVI FAQ里有这样一段话:

30. What is the difference between the TFP401 and TFP401A? The TFP401A includes HSYNC regeneration circuitry. This was required to be interoperable with the Sil154 that exhibited HSYNC jitter. However, the Sil154 is no longer on the market so most customers are now buying the TFP401

我现在使用的是TFP401A,有什么外围的芯片可以用来归整HSYNC 信号使它能够符合CCIR656 中的HSYNC 的规范,谢谢

我也要一份,634227759@qq.com。谢啦!

DVI FAQ这个文档比较老了,事实上,TFP401A内部集成了抑制jitter电路,在datasheet中也提到了:

The TFP401A incorporates additional circuitry to create a stable HSYNC from DVI transmitters that introduce undesirable jitter on the transmitted HSYNC signal.

你好,能发一份给我吗,先谢过了。我的邮箱:yhwz1010@163.com

加我QQ:634227759!

没有直接TFP401的原理图设计,其实可参考 TFP501的原理图:

http://www.ti.com/lit/an/slla134/slla134.pdf

我以前用TFP401做过一个DVI转VGA的转换器,下面是相关的资料与文档,楼主可以参考一下。如果想看原文,可以复制任意一段文字到Google中搜索:

DVI接收器选用TI公司的支持UXGA分辨率,最高输出165MHz像素时钟,支持全彩,支持每时钟输出两个像素,4倍超采样的数字接收器TFP401。

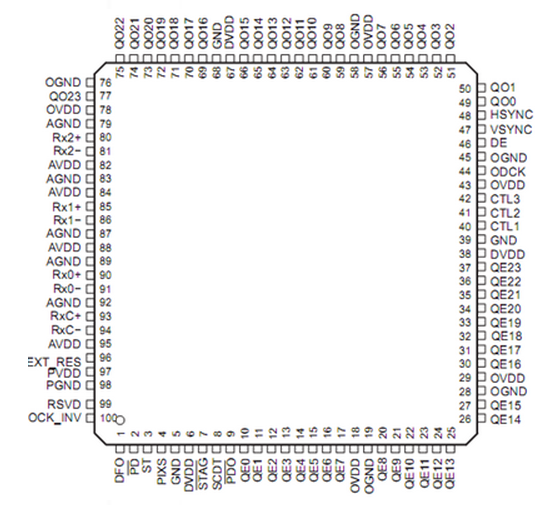

TFP401具有100个引脚,采用TQFP封装,引脚图如下所示。

图 3 TFP401引脚

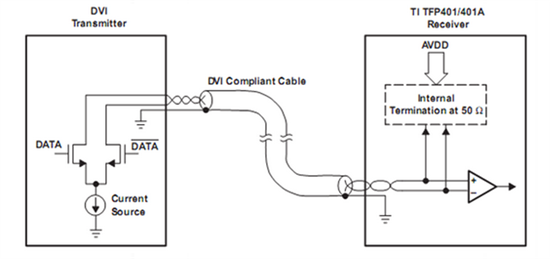

DVI信号通过DVI传输线缆传送进入ZV02,结构如下所示:

图 4 DVI线缆连接方式

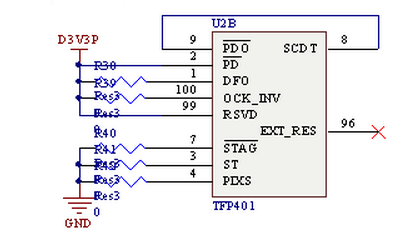

TFP401的配置电路图如下所示。

图 5 TFP401配置电路

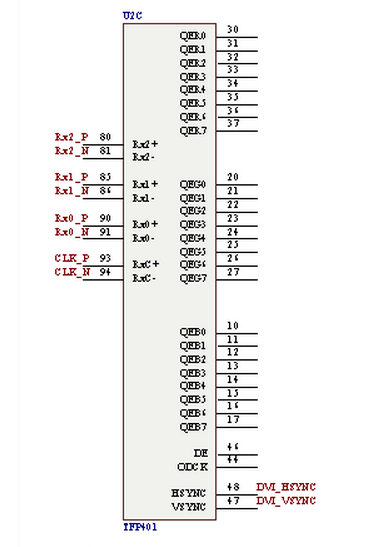

TFP401支持单周期双像素输出,所以一共具有48根数据线。而在转换的过程中,不需要使用双像素输出的功能,所以只需要连接奇数像素的24根数据线即可。具体连接如下所示。

你好,能给我发一份参考资料吗?liangxiaojun214@163.com

参考楼上资料即可

你是说的这个设计的设计文档么?设计文档已经发给你了。

TI的哥们可以给我也发一份TFP401A的外围电路参考图么,邮箱mhdcqu@sina.com 先行谢过

请问你在设计过程中遇到什么问题了呢?

请问单周期双像素是什么意思?奇偶像素的区别在哪里?奇偶像素分别到两个显示屏可否形成3D效果?谢谢!

请问是否能够将奇偶数据线各挂一个RGB接口的LCD呢?