设计的放大电路做出实物以后,放大倍数比原理图仿真的时候偏小

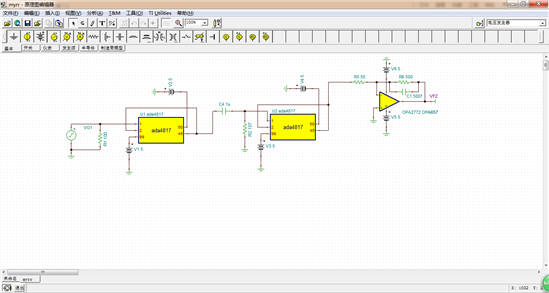

如题,设计的放大电路倍数为10,做出实物以后,放大倍数却只有7,倍数从几十K到几十兆比较稳定,但都偏小。仔细检查过,元件没有焊错。原理图仿真的时候,也是正常的,好好的。

我也尝试过加大反馈电阻,放大倍数确实提上去了,但还是偏小。16倍,实际的就只有10倍。不知道哪出了问题,所以发帖求助一下...

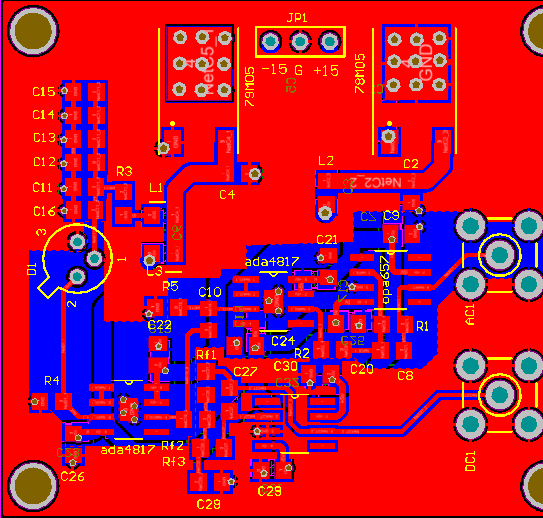

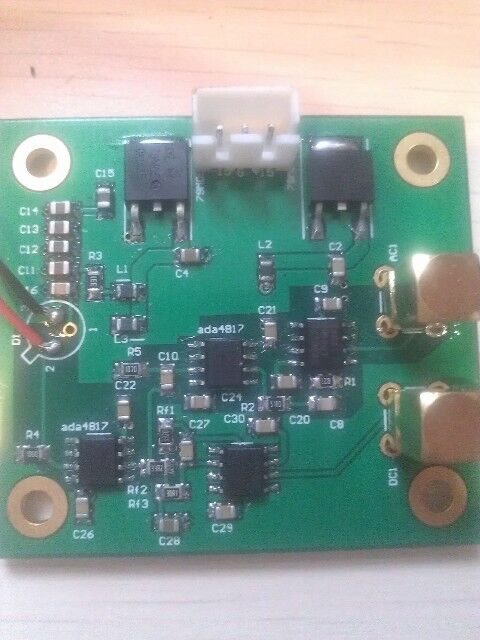

上面是画的pcb两层板的 信号层

亲;你的测试信号多大?建议测一下小信号时的增益。

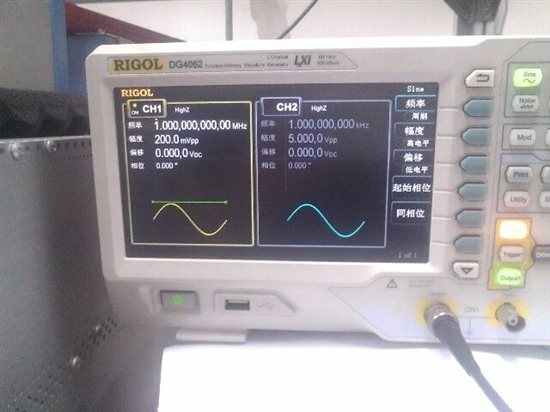

输入信号是200 mVP-P,放大十倍应该有2 VP-P,从50kHz到28MHz,输出都是1.4VP-P左右。到30MHz变成1Vp-p,到32MHz又变成1.3VP-P这样。

您说的小信号,是指的输出信号是200 mVP-P 吗? 还想问个问题,信号发生器产生200 mVP-P的正弦信号,可是到第一级运放输入那实际的只有180 mVP-P,

400 mVP-P就只有320 mVP-P。我是在板子上焊两根导线出来接信号发生器的。。 对这个很不理解。

亲;小信号指10mV左右级别的信号。建议测一下这时的增益。

额,在低频的时候,比如1M,小信号和大信号输入的话,放大倍数也不会相差这么大吧。。。

亲;这可不一定,需要了解发生问题的原因。

如果小的不多就是可以理解的,这个主要实际电路并非是理想器件,负载阻抗不同,都会影响输出。

TI精密实验室放大器教学视频好像说有些情况下和带宽有一点关系,供参考。

仿真时的结果和实际硬件的实验结果略有差异,是正常的。

有时候方法倍数也会偏大一点。

设计的不够合理,或者用的器件参数有限制,可以先搭一个电路出来,多放几个级,直到得到自己想要的放大倍数。

小信号指10mV左右级别的信号。建议测一下这时的增益。

仿真只能算仿真,还是实际电路来得确切。。还能改电阻

仿真的结果只能做参考了,还是以实际为准吧,电阻精度,温度,片子本身差异都有影响,建议看一下电源电压纹波

请检查原理图中一级和二级放大电路之间的耦合电容参数是否合适?

有点多额,10倍实际得到的只有7倍。 改了反馈电阻后,16倍实际的只得到10倍。。

第一级的跟随电路,第二级的高通滤波,这两个之间滤掉几十k(50KHz)以下的低频信号。。 这个有其他的影响不?

仿真的结果只能做参考,以实际为准,但不能差太多

不知道楼主在实际电路的各级放大器上的供电电源电压如何实现的?具体没碰过这种情况。

50欧电阻太小了,驱动能力可能不够,加大点试试

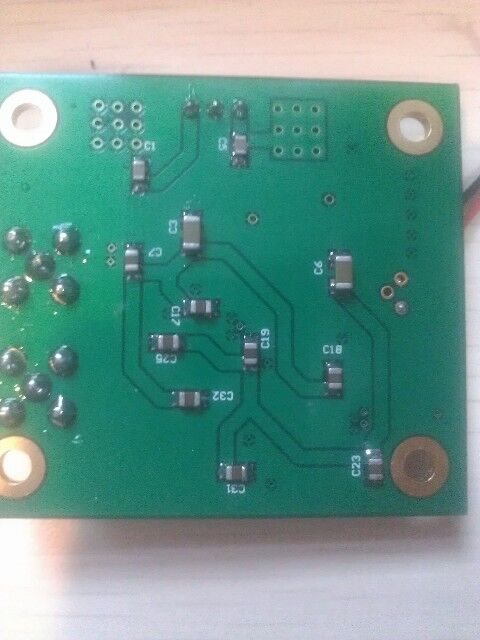

正负7V供电啊 上面的图是电源布线。 运放供电都接一个10u和0.1u的电容

谢谢,我换大一点的电阻试试。

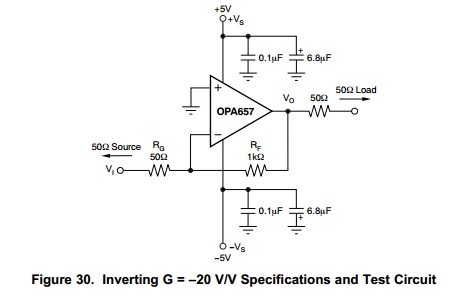

去掉C1,按手册上的电路仿真一下。

二级运放是高通滤波,信号会衰减的!与输入信号频率以及运放的带宽都有关系的! 建议在这级加入负反馈放大。

额 现在的板子在第二级运放那没反馈电阻,。。

去掉C1后,仿真出来,电路增益为25.99db.. 没到20倍的放大倍数额

搞错了 ,仿真出来的就是20倍。。

会不是器件的容差导致的,但是容差也不会差这么多,再仔细看看什么原因

仿真和实际设计的出来的是有误差的,不错差的有点大,看看器件的参数设置。不然这个也是可以接受。

可能运放的带宽不够

看你的PCB不是按照仿真图画出的吧。如果仿真正确,测试有问题的话,考虑布线和元器件选择。

高频电路信号最好走1字型,上下都铺铜了,可能与信号焊盘组成小电容,这个仿真时得考虑。

正常,仿真都是很理想的情况,实际电路都会有损耗,

同一批元器件还有差异性呢,一般设计时会稍微提高放大倍数,

以抵消这部分损耗,建议阅读【晶体管设计】,里面有介绍放大器

的设计,内容有提到过这一点。

不是... TINA软件里是简化的原理图,电源供电部分等都是用AD软件画的,这部分TINA也没法仿真。。

确实比较奇怪。看看有没有其他人遇到过,也学习一下时如何处理的。

个人分析有一下几个原因:

- 有效带宽;

- 电阻的精度和一致性,要选择高精度电阻以及功率;

- PCB布线的影响,合理的布线很重要;

- 输入信号的类型和质量;

- 原理图设计,合理的原理图设计同样非常重要;

在带宽范围内吗?

仿真属于理想状态下的,实际中元件阻抗、PCB布局都会影响结果。提高下增益看能否得到你想要的放大倍数

加大反馈电阻,确实能提高放大倍数,这个我尝试过。 510欧的电阻(10倍)可以得到7倍, 820欧的电阻(16倍)可以得到10倍。

在带宽范围内,选用的运放带宽都是至少大于400MHz的。

这个电路是做光电放大电路用的, 在接二极管那引两根导线出来接信号发生器,一根信号线,一根地线。输入的是电压信号,200 mVp-p.

c1,c4这两个电容看看有没有问题,看看在实际电路调整一下,看看会不会减小误差。

大秦正声讲的有道理,按他说的试试.

比理论值小:电路本身的功率损耗等

失真原因:运放进入非线性区等

我试试吧... 做的板子在二级运放那就只弄了高通滤波,没加上同相放大...

不是很理解二级运放作为高通滤波为啥对信号有衰减,能答下疑不?

仿真本来就是理想状态下的估算,与仿真模型有直接关系。

电路受到各种参数影响,会有较大差别。看看仿真模型的参数设置情况

R,C尤其电容并非理想器件,信号通过会有一部分损耗的! 你的实验数据说明同样电路信号频率越高,得到放大的幅值越小! 选择质量好的电容和参数,效果会好点。

1.检查增益带宽积,看他的曲线,也许在某个区间(低频或者高频、一般在高频出现,又是低频或者高频突然增大再衰减),导致放大倍数出现误差。

2.PCB布线也存在阻抗问题,线越细,阻抗越大,导致误差,当然布线也会引起连锁反应导致误差。

3.线路之间耦合,检查每一级输入输出是否存在衰减,逐一检查、排除。

4.看R、C器件,估计在某些频段会有损耗信号,用示波器测一下,同时选用容抗较小的电容,减少信号线长度。

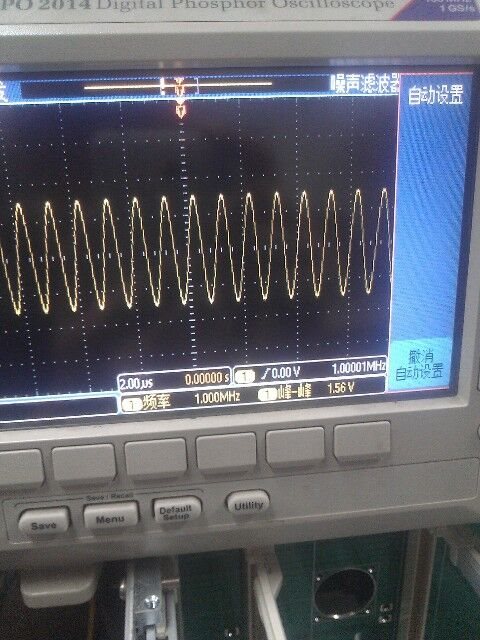

从50KHz到28MHz输出都比较稳定...

波形不失真吧?! 把示波器测量的波形拍成照片传上来看看。

好工具! 好波形!

这应该和系统的输入阻抗有关系 如果是小信号的话 很容易出现放大倍数比预期小的问题

是不是没有用精密电阻,就是千分之一的那种

千万不要以仿真结果作为标准来评估你的电路实现,累死也实现不到仿真效果。

以满足你的需求为基本前提来测试电路。

还想问个问题,信号发生器产生200 mVP-P的正弦信号,可是到第一级运放输入那实际的只有180 mVP-P,

这个比较奇怪,能把你的实际电路贴出来看下,

高频端接的阻抗一般是用50欧姆(信号发生器输出阻抗为50)减少信号反射。

这个与设计电路,PCB布线,芯片制造工艺,环境条件,输入信号都有关系,建议严格按照芯片参考资料进行设计应用。

一个放大器应该考虑实际的带宽增益积的情况,频率越高他可能放大倍数就会降低了,另外还有1DB压缩点也要考虑输入的功率的影响,还有,我一直觉得不要以仿真为参考,因为实际算出来放大多少倍为参考。

是高频有衰减么?可以先检查下板子布线布局会不会对信号线有影响。