CDCE62005无法锁定

大家好,我正在调CDCE62005遇到了一些问题,忘大家不吝赐教

我的板子上用了一片CDCE62005,只有25MHz的晶体输入。我想获得一路100MHz、一路66.67MHz的LVDS时钟输出。

遇到的问题如下:

1. 由于CDCE62005内部有默认的寄存器值,我直接发SPI写寄存器5,将输入改成Aux IN,即25MHz的晶体输入。结果发现CDCE62005的每一路都有时钟输出。同时我再写寄存器0-4的Output Divider,发现输出的频率能相应变化。但是,CDCE62005不锁定,输出的频率很不稳。想问一下,25MHz晶体进去,输出100MHz、66.67Mhz,怎样才能让CDCE62005锁定?

2. 为了让CDCE62005在输入25MHz晶体的时候能够锁定,我改了寄存器6中的Lock Window,把Lock Window改到最大28.6ns。结果发现CDCE62005还是不锁定,虽然CDCE62005的每路都有输出,但是很不稳定,PLL_Lock引脚时钟为低电平。请TI的FAE确认一下,CDCE62005手册的第66页Digital Detect Window是5.22~5.25,还是5.23~5.26。

3. 我尝试着读内部寄存器的值,结果发现,我无论发读第几个寄存器的值(比如0000005E,读第5个寄存器的值),SPI的MISO时钟捕获的结果始终是CDCE62005的第0个寄存器的值(8184032),我的SPI写操作应该没有问题,因为我对每一路的output divider都操作了,输出的频率能够相应变化。但是遇到了SPI读CDCE62005这样的问题,不知问题出在什么地方。

1. 首先CDCE62005在25Mhz参考输入时,不能同时输出100M和66.67M,这个需要小数分频。这个你可以通过网上去下载CDCE62005 EVM评估软件来计算,地址如下:

http://www.ti.com/tool/cdce62005evm

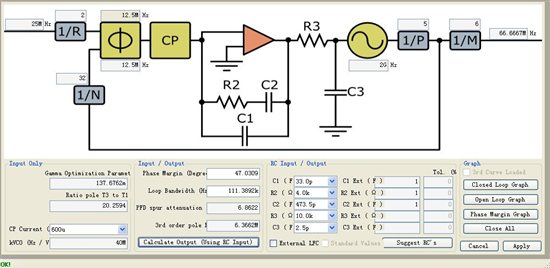

2. PLL要正常工作,不是简单配下输入和输出就ok的,还需要配置内部VCO频率,PFD等等。

如果你需要100MHz和66.67M同时输出的话,建议考虑TI新一代的时钟CDCM6208,小数分频就可以实现你的需求。

http://www.ti.com/product/cdcm6208

CDCE62005在25MHz晶体输入的情况下,是可以同时输出100MHz、66.67MHz的吧。比如,VCO锁定在2G,VCO后面的Prescaler分频为5,这样的话,进入Output Block的时钟就是400MHz。然后一个通道Output Divider设置为4,则输出100MHz;另一个通道的Output Divider设置为6,则输出66.67MHz。

这个我是参考TMS320C6678的EVM设计的,肯定能达到1000MHz、66.67MHz同时输出的。

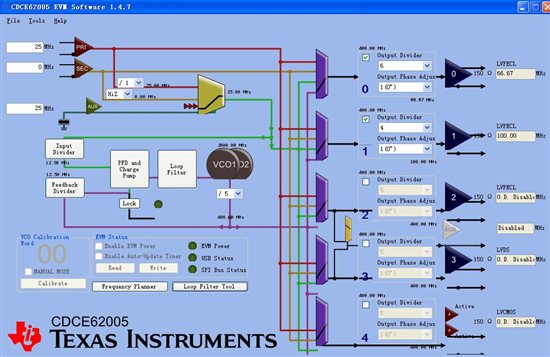

我的配置如下,您看看能不能锁定

我的问题是:按照这样的设计,怎么判定CDCE62005 PFD的detect window够用,从而锁定呢?

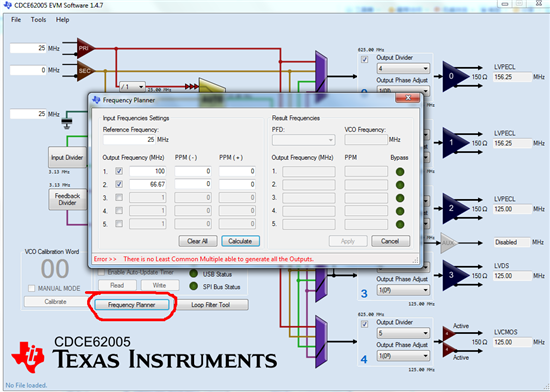

从CDCE62005软件可以做frepuency planner,是无法做到100MhZ和66.67M同时输出的。

如下图:

其实关于这点我跟你有同感,直接设定频率是不能同时输出100MHZ和66.67MHZ,但是实际在寄存器的配置中是可以设置的 如果我没有记错,输入为25MHZ,按照F=128 P=1 R=8 O=6可以实现 66.67MHZ,100M则是F=128 P=1 R=8 O= 4即可

除了看分频系数是否能满足之外,还要看VCO的频率是否满足,也就是说在满足VCO频率范围内来设置分频系数,建议直接采用CDCE62005的GUI软件,将输入输出频率填写进去,看能否通过合理的配置得到想得到的输出频率,建议参考之前讨论的类似帖:

http://www.deyisupport.com/question_answer/analog/interface_and_clocks/f/59/t/68187.aspx

其实感觉你还没有明白我说的意思,就是软件要配置这个66.67MHZ,是配不出的,但是通过自己的寄存器配置就可以,简单来说就会GUI软件还有BUG,不能完全匹配某一些频率,而实际上又可以产生。

其实对于TI员工说的无法配置我也是很奇怪的,因为在C6678开发板上,关于CDCE芯片的配置,在datasheet以及电路图中明确给出的就是100跟66.667,如果无法配置,那datasheet肯定不应该那么写了!

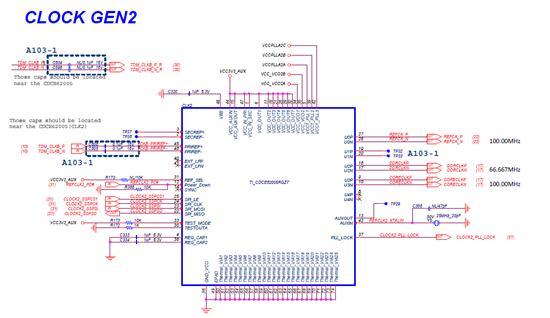

对于这个直接配置出来的100跟66.67,我有一点想请问您的是,就是关于PRI跟AUX的问题,一个例子就是C6678 EVM开发板的一个CDCE62005时钟芯片,其自带原理图如图所示

如果要通过软件设置让其产生100与66.667的时钟,那么在软件界面设置中参考就相当于上面帖子Feng Jin所配置的一样。

我有几个疑问

1.就是在Smart Aux选择模式是AUX也就是25MHz晶振的情况下,软件中PRI时钟的大小设置应该参照什么,是不是Smart Aux选择模式是AUX后,PRI模式输入时钟的计算就只起到辅助产生100与66.667时钟的作用,而与实际上这个端口输入的时钟大小没有关系?

2.VCO的大小变化是根据什么来的,每次设置时他都会变化好多次?

不知道您方不方便留一个联系方式!

您现在问题解决了么?能不能咨询求助一下!

还想请问您,您说的F、P、R分别代表什么啊?