lmk锁定指示问题

目前系统中使用1片lmk04808,

输入时钟频率:125M;

VCXO频率:125M;

PLL1相关配置参数为参考设计给定值:

Mode:Dual PLL, Internal VCO;

PLL1_WND_SIZE : "11";(40ns)

PLL1_DLD_CNT:0x400(1024)

PLL1的外部环路滤波器参数是参考设计给定的为:

C1:0.1uF;C2:0.68uF;R1:39K;

问题:在上电配置完成后,发现PLL1不是每次都会锁定,即在配置相同的情况下,有时上电可以锁定,有时无法锁定(通过PLL1_DLD引脚观察),这是为什么?(PLL2始终可以锁定)

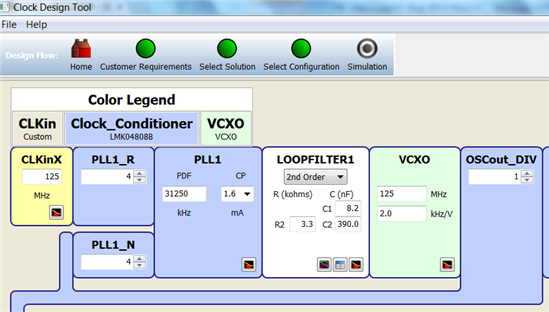

你的鉴相频率是多少?我这边软件得到的环路与你的不一样,请参考:

你好:

我鉴相器频率为1Mhz ,PLL1_R和PLL1_N都是125,请问这是什么软件,哪里能下载到?谢谢!

clock design tool

你可以在TI的网站上免费下载。他提供LMK,LMX系列的全套仿真,包括环路滤波器的设计

clock desgin tool的全套软件可在以下链接中下载:

http://www.ti.com/tool/clockdesigntool?keyMatch=clock design tool&tisearch=Search-EN

你可以提高鉴相频率看下,是否稳定锁定。我用的CLOCK DESIGN TOOL下载地址如下

http://www.ti.com/tool/CLOCKDESIGNTOOL

你好!

我按照软件中的参数换了环路滤波器的电阻电容

现象和之前的一样,而且发现换滤波器上没有阻容 有时PLL1也可以锁定,这是怎么回事?

另外,在锁定指示为低时,使用示波器测量CPout1引脚,上面有1.5V左右,比较平滑的电平信号。

请问,锁相环的状态能否通过CPout确定,CPout平滑到什么程度,才能说明我的环路滤波器设计没有问题?