CDCE62005芯片配置

时间:10-02

整理:3721RD

点击:

你好:

我们板子中选择时钟芯片CDCE62005作为主时钟,输入为:61.44MHz,希望输出为:122.88MHz、153.6MHz、和184.32MHz。

请问是否可以实现,配置参数是多少?

我用CDCE62005这个芯片带的计算软件算不出相应的时钟来,而这三个时钟又都是30.72(61.44/2)的倍数。感觉上应该能配出来才对。

麻烦帮我看下,谢谢~~

你好,时钟输入输出要满足datasheet上的第11页的几个公式才行,因为它并不是单单分频和倍频的问题

你好,122.88MHz、153.6MHz、和184.32MHz的最小公倍数是1843.2M. cdce62005的vco可以跑那么高但是由于有prescaler所以总线上到不了那么高的频率.

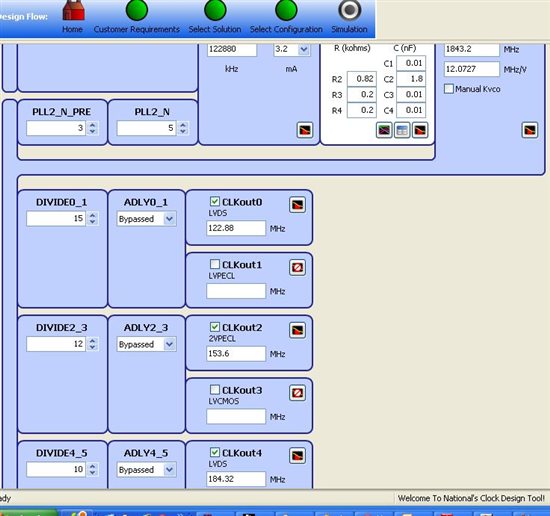

目前只能用lmk04803同时产生这三个频率,具体配置如下,用clock design tool即可得到: