SN65HVS880 的时序问题

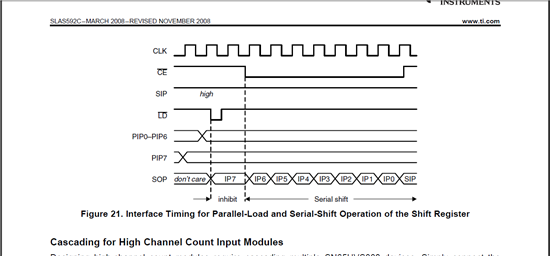

1)上面SN65HVS880 时序图,有点不太明白,为什么SOP的第一位IP7在使能信号CE变为低电平时就被传送出去了,而且下面写着inhibit,是不是说IP7是被抑制

掉了,因为我在用一个SN65HVS880调试时发现当我没给并行口数据时,串行口接收到的数据总为0000 0001。

2)给IP7高电平时,数据时加载不到串行口的,其它的6个并行口能加载到,0000 0001中的最低位中的1是不是因为没串接下一个SN65HVS880引起的呢?是不是

一个完整的8位数据时IP6 IP5 IP4 IP3 IP2 IP1 IP0 SIP,而不是IP7 IP6 IP5 IP4 IP3 IP2 IP1 IP0?

3)还有一个问题是SN65HVS880是不是在CLK的上升沿发送数据出去的?

谢谢。

figure21似乎是有点问题。 CE\变低后的CLK的第一个上升沿对应的SOP应该是IP7。LD\为低,是将IP0-IP7的值锁存到相应寄存器。LD\为高,IP0-IP7 pin的状态不会影响相应寄存器的值。

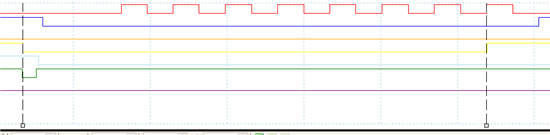

上面的时序图是我用C2000实际调试时测出来的 —— 红色:CLK 蓝色:CE\ 黄色:SOP 绿色:LD\

上面的时序图基本上是跟文档上的一样的,可以发现当LD\ 一变为低电平时并行数据立刻被加载,当LD\ 变回高电平后在CE\使能后的CLK第一个

上升沿时IP7已经被传出去了,如果有连接下一个SN65HVS880,IP7应该被加载到下一个SN65HVS880的IP0里。而在CLK的最后一个上升沿接收

到了高电平数据,我想这样 “1” 应该是SIP上接收到的上一个SN65HVS880的 IP7 位的数据。而由于我现在只用了一个SN65HVS880,SIP引脚被

悬空了,被默认为高电平了。

我是这样理解的,不知道对不对。不过如果是这样的,那么我只有一个SN65HVS880时,那 IP7 这个通道不就没用了吗?一个SN65HVS880有

8个并口,但实际上能用到的只有IP0 —— IP6这七个呢?不知道是不是这样的

肯定是8个位的。给出PIP0-PIP7 这8个pin就是8bit。

看下datasheet第11页的figure15 shirf register logic structure. 根据这个图以及时序图,当LD/下降沿变为低后,第一次读SOP的值,这个值就是IP7的值。CE变低后再在CLK 上升沿后读SOP的值就是IP6的值。没有错了。你既然搭起了实验环境,可以验证下。

按你说,那就是说我的测试结果是正确的?