急! 问,为何通过Vctr来调节CDCE913输出一个锁相时钟,一直不成功。

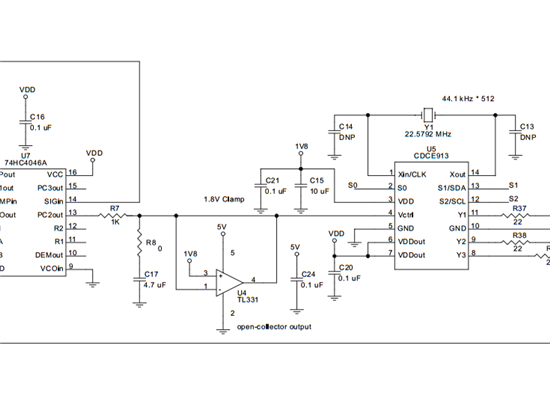

大家好,我用cdce913芯片,XTAl用的是25M的4角晶振。通过FPGA用IIC配置Y1输出的也是25M。然后把Y1输出的25M,和另一个RTL8201芯片输出的25M时钟,同时输入FPGA,通过FPGA将这两个时钟分频成10K的时钟。下图一,是CDCE913的参考电路,我只是用FPGA替换了74HC4046A。两个分频后的时钟相比较用的是图二的方法。但是配置完后用示波器测量发现从CDCE913出来的时钟25M不是很规则,很多毛刺,而且根本没有和RTL8201芯片输出的25M时钟锁相。

不知道问题出在哪里,是不是FPGA的IIC没有将CDCE913配置好,还是什么原因,看了很久的手册,不知道从哪里入手了。望指点。我还需要补充什么没讲到的么?

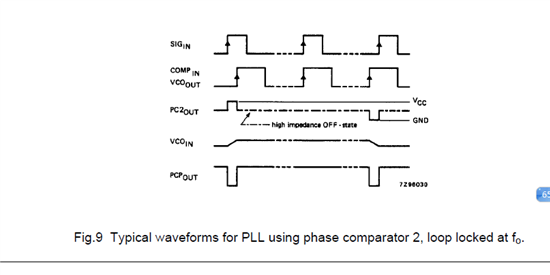

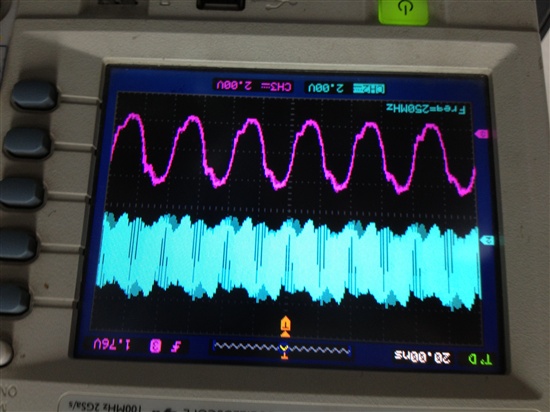

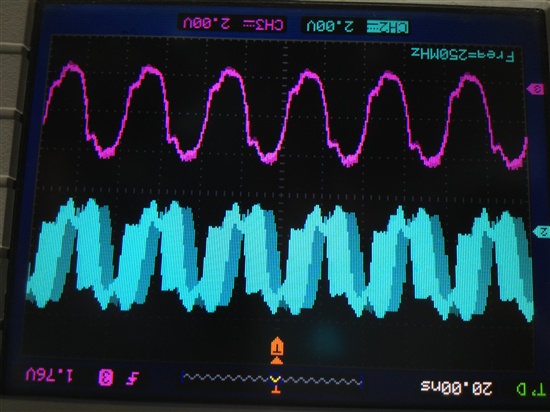

我用一个25M的4脚晶振作为Xin,将他从Y1输出的25M时钟,和我RTL8201芯片输出的25M时钟同时输入FPGA,在FPGA里面将两个25M时钟都分频为10K的时钟来比较相位,当CDCE913时钟分频出来的10K时钟,上升沿滞后时FPGA输出给Vctrl的信号变高,超前时信号变低,其他时候为高阻态。但是用示波器观察发现,Y1输出的时钟根本就没有和RTL8201的时钟锁相。而且时钟还不规范。请帮忙解答一下。

有没有具体的波形?另外你的寄存器配置?

你好,感谢你的关注。下面我将我的信息一一列出来。

1.我是通过FPGA写的IIC程序对CDCE913进行配置的。因为我只是需要输出一个锁相时钟,所以只配置了offset 00-06.下面是我的配置。

问题:1,不全部配置,CDCE913能正常工作么?

2,我怎么检测我用IIC协议配置CDCE913成功。

//--Slave Receiver Address

parameter Slave_address = 8'b11001010;

OFFSET //--Command Code Definition | Data Byte

00 8'b10000001; | 8'b00000100;

01 8'b01000000; | 8'b00000100;

02 8'b10000010; | 8'b00110100;

03 8'b10000011; | 8'b00000001;

04 8'b10000100; | 8'b00000010;

05 8'b10000101; | 8'b01010000;

06 8'b10000110; | 8'b01000000;

2,下面是我在用Signaltap 抓取的信号,注意看"pahse_error","phase_error_polarity""phase_cdce913""phase_rtl8201" "TEST_CLK""cdce913_25M_i" 这几个信号。他们之间的关系式这样的。TEST-CLK信号是输出给Vctrl脚的信号。就是像我第一个帖的图一样。当RTL8201的波形超过CDCE913的波形时,TEST-CLK为高,落后时为低,其他情况为高阻态。

问题:1,看下面第2张图,为什么当TEST-CLK为高输给Vctrl时,CDCE913有一段时间是没有时钟的?

assign phase_error = phase_cdce913 ^ phase_rtl8201;

assign phase_error_polarity = phase_cdce913 && (!phase_rtl8201);

if (phase_error )

begin

if (phase_error_polarity)

TSET_CLK <= 1'b1;

else

TEST_CLK <= 1'b0;

end

else

TEST_CLK <= 1'bz;

3,下面我给出我用示波器同时测量锁相后的CDCE913和RTL8201,25MHZ 时钟。可以看到他们两个没有锁相成功。

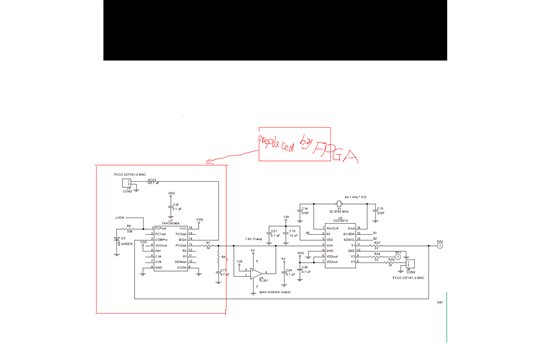

4,我用的是芯片手册里的推荐电路,应该是没问题的吧。

请问还有什么要补充的么?

期待你的答复,谢谢了,托了很久了。

您好。我补充的内容全部上传上来了。能麻烦关注一下吗。

大神,有木有在呀,求关注啊,我等到花儿也谢了啊。。