请问TI有带锁相环功能的3.3V-2.5V双向电平转换芯片吗?

您好:

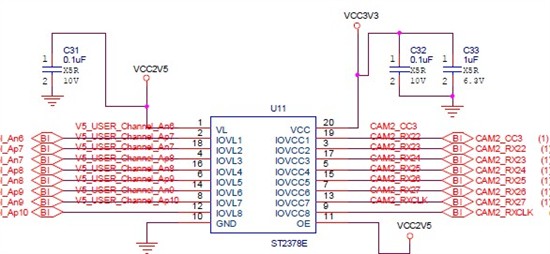

我们在做图像处理的时候需要用到一款电平转换芯片,

如图,左边的信号是连接到FPGA上的,电压是2.5V,右边接的是采集到的3.3V TTL/CMOS信号,有控制信号、数据信号和时钟信号,速率是80MHz

然后我们现在选用的芯片一个是电平转换延时较大,另外一个是输出输入信号延时不一样,我们担心会造成相位不一致的问题

然后想请问各位TI的专家,TI电平转换芯片里面有没有带锁相环的电平转换芯片,或者能够保证稳定延迟的电平芯片,即保持输出信号跟输入信号的相位差固定的电平转换芯片,能够满足上诉的功能,如果有,请推荐一种型号,

谢谢

3.3V和2.5V电平转换的器件很多,但没有带锁相环功能的。其实你的意思就是需要一款8bit 3.3V和2.5V双向电平转换器件,TI的电平转换输入输出传输延迟很小,一般在ns级别。输出也输入的差异就是仅仅有一个很小的传输延迟,相位不变,相当于一个buffer。能满足80MHz频率的话 SN74AVC8T245这款就满足您的需求。

http://www.ti.com/lit/ds/symlink/sn74avc8t245.pdf

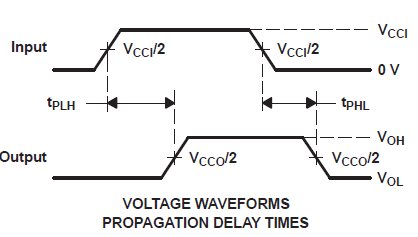

补充一下,电平转换都会有时延,一般用tPLH和tPHL表示,如下图。从你的应用来看,时延可能不是太大问题,如果时钟和信号都经历同样时延,最后时钟还是有足够的setup time和hold time来锁住数据。可能这种应用更多的是关注channel-to-channel skew,就是通道间时延的最大差别,比如1号通道延时最小,0.1ns,8号通道延时最大,2ns,那么skew就是1.9ns。Kailyn推荐的芯片没有skew数据,不过skew肯定是落在最小tPLH和最大tPLH之间。从手册第7页看,VCCA=2.5,VCCB=3.3,从B到A时,tPLH(或tPHL)的范围在0.5~2.9ns,就是说,skew不会大于2.4ns。这个skew,会影响setup和hold time,可能实际应用时还需要在FPGA侧调一下时序。

谢谢Decapton的补充,非常有帮助。

Decapton Wang

您好:

首先非常感谢您的回答

您提到的这个问题是我担心的问题,80M的传输速率的周期是12.5ns, 对于ns内的延迟来说时钟是会有足够的建立时间和保持时间来锁住数据,然后在帖子我没有把我的观点表达清楚,我担心的就是channel-to-channel 的时钟偏移(skew),由于我们用了2个同样的相机进行图像采集,然后2个相机的数据都通过电平转换芯片接到FPGA中,比如相机1用的是转压芯片1,相机2用的是转压芯片2,当2个相机对同样的场景进行采图时,用同样的转压芯片采集,担心的有2个方面的问题

1.对采集到相同图像的数据发送端是同相位的,通过转压芯片后,对于这两个一样的转压芯片,输出的相位是否能够保持一致,由于Tplh是0.5-2.9ns,是一个时间范围,那样的话就存在输出信号相位不对齐的问题,这个相位的不对齐采图的控制时序,发生采图问题?

2.第二个问题其实跟第一个问题差不多,是存在同一个转压内部的问题,对于同种类型的传输信号,比如数据信号,由于不同channel的延时,最终输出到FPGA中的时序会略有差别,这会对FPGA的信号处理产生多大的影响?

p.s:之前那个工程师推荐的SN74AVC8T245 这款芯片适用于这种情况吗?如果适用,原因为何,有没有更好的方法呢?

谢谢

p.s:不置可否即时交流?

Kailyn Chen 您好

首先非常感谢您的回答

Decapton提到的channel-to-channel skew正是我担心的问题,请问一下这种情况下您推荐的芯片是否适用这种情况,有没有更好的方案呢?

谢谢

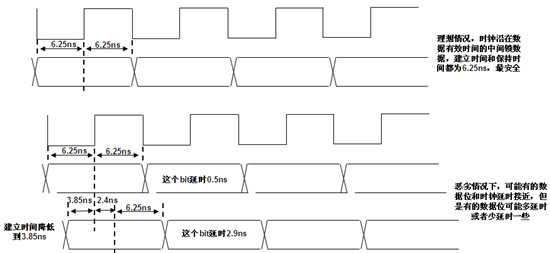

1. channel-to-channel skew是相对一片芯片说的,你说的两片芯片的问题,是part-to-part skew,同样手册上没有提供这类信息。对于80M信号,周期12.5ns,如果是SDR,时钟率和数据率都是80M;如果是DDR,是数据率可以达到160M还是时钟率可以降到40M?简单起见,以SDR为例,如果数据率是80M,时钟率也是80M,那么数据周期就是12.5ns,如果想时钟最可靠的锁住数据,时钟的沿应该在有效数据的中间,即距离数据两边6.25ns。现在考虑skew,由于Tplh是0.5~2.9ns,所以有可能时钟delay 0.5ns,数据线上某一位delay 2.9ns,即时钟跑到了6.75ns,最差的那个数据跑到了9.15ns。不过即使这样,最差的那个数据距离边界仍然有3.85ns的margin,即最小的setup time也有3.85ns,FPGA应该能够在这样一个3.15ns的时间里锁住数据。如果考虑part-to-part skew,除了芯片本身的指标外,跟layout也有关。layout上两片越对称,走线等长做的越好,skew越小。至于part-to-part skew对setup time和hold time的影响,可以按上面的方法做类似分析。一般来说,这种高速应用里都是直连的,很少有用到这种电平转换的。

2. FPGA里面都是带时钟和数据延时的吧?如果你觉得skew对你来说是个很严重的问题,可以在FPGA里调delay。比如最小的数据位delay 0.5ns,最大的delay2.9ns,你可以让时钟delay1.7ns (0.5/2+2.9/2),同样可以在一定程度上降低skew对数据传输的影响。

3. 以上分析就是以SN74AVC8T245为例做的,当然你也可以去找找看有没有更快速度的转换芯片,理论上说,速度越快的芯片,skew越低。