DS90C3202的IIC读取问题

最近在做一款DS90C3202设计。通过MCU配置DS90C3202的寄存器。写操作都没有问题,但是读操作会错误。

每次读操作的最后能收到MCU的NACK信号,但是之后DS90C3202的SDA信号就一直是低了,MCU的stop信号就接收不到了。MCU总线上还挂有EEPROM,读写EEPROM都没有问题,很奇怪。不明白为什么每次的读操作收到NACK以后为什么SDA会一直被拉低呢?苦恼

每次断电重新上电后似乎写好的寄存器值又恢复到默认状态了,这是为什么呢?

我现在找了一块板子,只有MCU和ds90c3202,发现读操作还是有问题,每次读操作的前面一切正常,就是到了最后sda就被拉低,奇怪了。还有就是每次掉电DS90C3202似乎不保存配置信息,都恢复到默认状态了

3月1日:

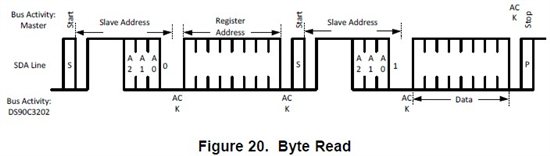

总结了一下目前的状态,写操作都没有问题,虽然datasheet里面提到只支持byte读写操作,但是连续写寄存器没问题,连续写8byte寄存器也不会出错。读操作的时候比较特殊。datasheet里面提到:

The data byte has the most significant bit first. At the end of a read, the DS90C3202 can accept either Acknowledge or No Acknowledge from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte).

在读操作结束的时候,3202能接收ack或者nack信号,典型情况下接收nack信号。

首先尝试发送ack信号后面发送stop信号。,3202会响应ack,并继续发送下一个byte的数据。这样接收不到紧跟在ack后面的stop信号,所以MCU停止发送时钟,sda也就被3202拉低保持在忙状态。

然后尝试发送nack后面发送stop信号。3202依然会响应nack,并发送下一个byte的第一个bit,然后就停止。如果下一个byte的第一个bit是低,3202依然接收不到stop信号,读操作结束的时候sda就被拉低并保持。如果下一个byte的第一个bit是高,那么3202就恰巧能收到mcu的stop信号了,这时候读操作停止,并且sda信号被释放,下次读写操作依然可以进行。

感觉3202在接收到mcu的ack或者nack后还要继续发送一个bit,然后再判断,如果是ack就继续发送,如果是nack就等待stop信号。另外就是每次掉电重新上电后3202的寄存器会恢复到默认状态,需要重新配置,如果不掉电,reset3202的话,那寄存器的配置就不会丢失。

不知道是板子设计的时候时序问题还是3202本身的iic接口有bug,ti的支持能不能解答一下?

这个属于已知 issue 属于MSP430和slave的I2C 通信协议有关,建议你发到MSP430 板块由相应工程师来详解。

我没用到msp430,用的就是一个简单的51单片机读写IIC。转过去被删帖了,还是在这问吧

这...

这方面在DS的datasheet里没有较多解释,不过隐约根据sequence可以发现是不需要no ack 信号的,请尝试直接发stp

如果采用MCU的GPIO口配置I2C的话,需要看下GPIO是否内部已经上拉,如果已经上拉,那么SCL和SDA外部则不需要再上拉

和MCU的IIC口应该没关系,MCU本身自带IIC口。我的IIC总线上挂了EEPROM和DS90C3202,读写EEPROM都正常,指示在操作DS90C3202的时候有问题。

datasheet里面写了可以发nack也可以发ack。我都试过不行。读一次以后sda就被拉低了,我把MCU复位也不能使sda拉高,只能重新上电才能拉高sda

51那边的I2C是模拟的还是标准的I2C接口?试着不要发ACK和NACK,直接STOP呢

可以的话用示波器看一下SCL和SDA 在两个通道的波形

没用,感觉像是有bug似的。51用的是标准iic口,应该不存在协议上的问题。发不发ack,直接发stop都不行。示波器波形看着很正常,如果是连续读取前面的byte数据也都对,就是到了最后接收不到stop信号了,sda被ds90c3202拉低了。很奇怪。

sda是被ds90c3202拉低的,不知道收到nack以后芯片进入什么状态了,会把sda拉低

补充一点,

1.你的EEPROM和DS是连接在一起操作的?

2.“sda是被ds90c3202拉低的,不知道收到nack以后芯片进入什么状态了,会把sda拉低”

--- 既然不发ACK/NACK都是这样,那这个就不应该是ACK造成的。还是请给一下后面SCL和SDA的波形看看,是不是SCL和SDA的配合收到干扰等。

已经排除EEPROM的影响,另外找了一块板子只焊接MCU和DS90C3202,单独控制还是有问题。

SCL的信号正常。SDA信号就是在主机发送了ACK/nack后就被拉低,没其他现象。SDA信号应该是被3202拉低的,因为我复位MCU以后SDA依然是低,断开SDA信号以后,3202一端是低,MCU一端拉高了

放大一下包含N/ACK之后SCL/SDA的波形

补充,NACK请分成你提到的两种现象

波形都没有问题,ack和nack都是正常的。暂时解决了一下,就是在每次读操作后面再读一个byte,nack发送两次,这样就能稳定接收到stop信号了。虽然不完美,不过也算是个解决办法,根本原因还没找到

还有困惑的就是每次重新开机后寄存器都要重新配置,在datasheet里好像没有提到3202的寄存器掉电丢失呀

1)3202掉电,寄存器值一定会丢失,需要从新配置。

2)上面提到的问题,是否上拉电阻值太大?建议4.7k。

谢谢回复,我现在用的上拉电阻阻值是2.2K,应该不是太小吧,变成4.7k应该就是沿的快慢变化,会有影响么?我试试

如果以前用2.2K,那就不是这个问题。建议找本地TI office,要块FLINK3V10BT-TX/RX,测试下。

先把问题结了吧,我再测试一下好了