时钟——LMK02000锁定时间及输出条件

本人最近用到TI芯片LMK02000最数锁相和时钟噪声出来,在使用LMK02000的过程中发现TI收购的美国半导体公司的2006年发布的LMK02000的数据手册和现在的数据手册中控制寄存器不同,请问这个从芯片上怎么看出是之前的芯片还是现在的?

还有一个问题,我现在初步测试了LMK02000芯片,发现LMK02000快锁定了,会出现有失锁,且频偏很大,这是什么原因引起的?还有一般情况下LMK02000锁定要所多长时间(滤波电路采用评估板电路)?还有出现一个奇怪的现象,只使能CLKOUT0时CLKOUT0正常工作,若将其他输出也使能的话,则全部使能的时钟输出都不工作,请问有人知道原因吗?

谢谢,期待回答!

Zhange,

请问你拿到的国半的数据手册中寄存器与现在的版本的区别在哪里?我对比了一下07年的国半的版本,寄存器上是一致的。

如果有不同,原则上是要遵循新的数据手册。

锁相环配置的问题你要规划和计算一下鉴相频率,相位裕度和环路带宽等参数。

附件的文章应该对你有所帮助。

NIck Dai 你好,

附件中是我下载到的一个美国半导体公司2006发布的datasheet。

目前这个设计中我用的参考时钟是10MHz,输出也是10MHz,N和R分频器相同就可以了,目前N和R分频器都是100(实际分频是100*2),鉴相频率为50KHz,寄存器的设置我参考了Codeloade4,根据我设定的要求,Codeloader4给我的和自己设置的值相同,鉴相后面的滤波电路我也用到了National Clock Design Tool软件,相位裕度为60,带宽为10Hz,按照这些设置锁相还是环不能锁定,且目前快锁定了之后有会出现跳动,这个过程一直反复。出现这个现象是什么原因引起的?

我也用PLL—MUX测试了写入的正确性,我将LD引脚通过PLL—MUX值不同强制置为高、低电平、N分频后的时钟、R分频后的时钟,都是正常的,且置为时钟输出时输出信号质量都很好。

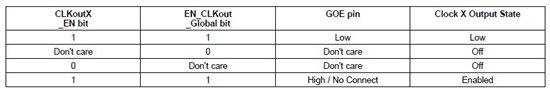

还有之前说过的只是使能的CLKOUT0的情况下,CLKOUT0的输出正常,我试过了几个分频数输出都是对的,但是当我使能了其他输出之后,所有的使能的输出都不正常,且都是1.6V的直流电平,这个是什么原因引起的?是不是一定要带负载或者什么其他的控制寄存器和相关引脚能够影响输出?但是奇怪的是只使能CLKOUT0的时候是正常的!

Zhangge,

数据手册请以最新的版本为准。

对于失锁的问题,请首先查看参考时钟的状态是否稳定。如果参考时钟稳定,请尝试改变鉴相频率,环路带宽等参数看是否能锁定。

时钟输出的问题请确认时钟输出的配置是否正确以及SYNC管脚的状态。

LVDS类型的输出在off状态下会输出一个1.5V左右的直流电平。

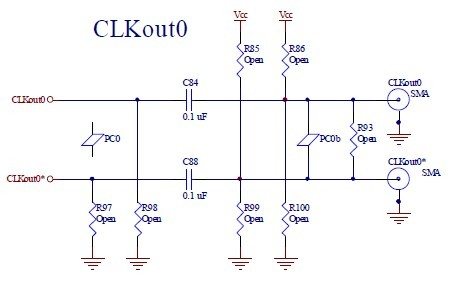

目前我调整了LVPECL输出的负载电阻,现在所有的LVPECL能够正常工作,使能一个或者多个LVPECL输出都正常工作,但是LVDS的输出全部不正常了,LMK02000的LVDS输出在差分输出之间单只接一个100电阻,没有接其他的负载LMK02000的输出能够正常工作吧!

LMK02000输出接SN65LVDS32没有没有问题吧,中间就只有在差分输出端之间接了100电阻

下面的电路是开发板上CLK0的输出,应该不需要接匹配电阻,你可以按照这个电路试一下。

如果接SN65LVDS32,在AC耦合的电容后面差分接100ohm电阻就可以了。

我用的是上面的电路,在LMK02000的LVDS输出端,我试了在AC耦合之前和之后接100ohm电阻,输出端都没有信号。好像都是off状态,输出为DC1.6V。

调试过程中我发现那个N Divider Output/2通过LD引脚输出,有时候没有,有时候输出频率跳动,有时候是正常的,这是什么原因?是因为输入信号的上升沿不够抖还是什么其他原因啊,

输入端用的是SN65LVDS31的LVDS信号通过交流耦合给Fin、Fin*输入端的