ADS1198采样率问题

采用STM32读ADS1198数据,读取的数据很正常,配置寄存器,配置采样率为500SPS,采500个点时间理论为1S,我却花了4S;配置成1K采样率,采500个点时间比之前稍微少了点,但也是4S左右,感觉采样率不受我控制。

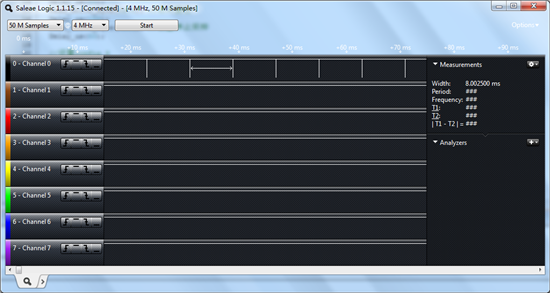

采用逻辑分析仪分析DRDY时序,采样率为125SPS时,时序为下图。

125SPS采样率DRDY时序

采样间隔时间为8ms,没问题,而且差不多都是这种间隔。

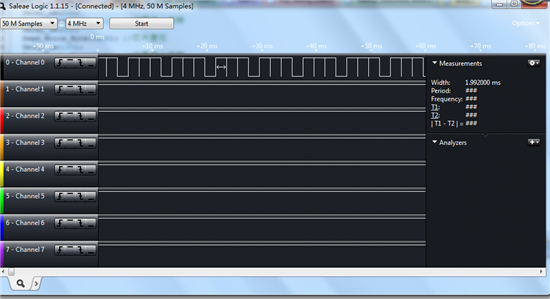

当设置采样率为500SPS时,DRDY时序图为

采样率为500SPS时DRDY时序图

发现时序图很不规整,有的间隔2ms,有的间隔9ms,而且时序图形状与125SPS完全不同。

可以看得 DRDY 的波形不规整, 但没有给出通信的其他信号波形. 根据手册

DRDY goes low when new data are available.

DRDY returns to high on the first SCLK falling edge.

再检查一下你的 SPI 通信波形吧

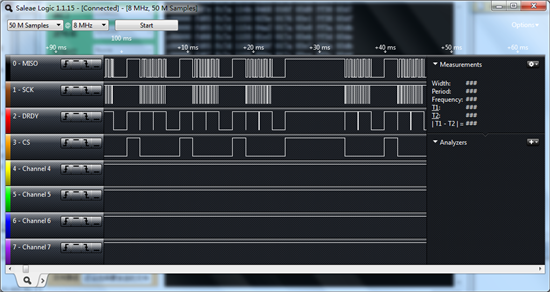

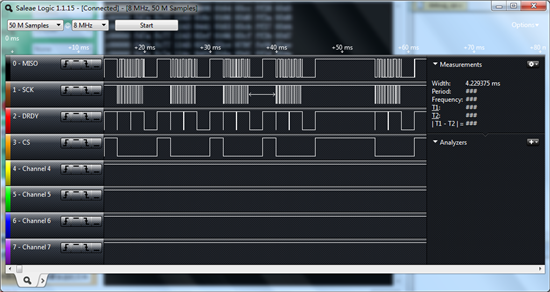

下面是我做的SPI时序分析

125SPS

500SPS

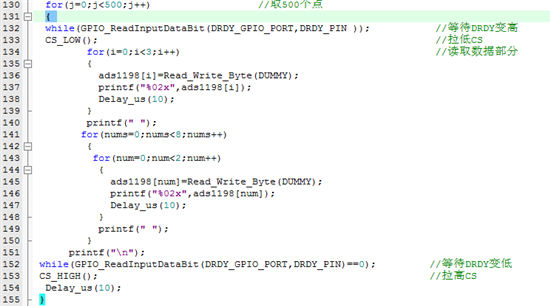

读取数据代码

我的SCK时序中间有很大的空隙有没有问题?

看我的程序,每读一个点的数据CS都要拉低,再拉高一次。如果CS一直置低,for循环500次,只有第一次有数据,其余的几次都是0。

采500个点,用for循环对吗?