ads1158读取数据的问题

时间:10-02

整理:3721RD

点击:

我现在用的ads1158在读取数据的时候,通道号是可以正常读取的,但是后面两个字节的数据读不到,不管输入信号怎么变化,读到的两个字节数据始终是一个固定值不变。这是为什么?

初始化配置程序没有问题吧

这个应该没问题。通道号能读取,我换不同的通道号都可以正确读取,这是否可以说明初始化没问题?

在读数据的时候,按理说new位应该为“1”,我的始终都是“0”,

读之前有没有检测DRDY是否有效

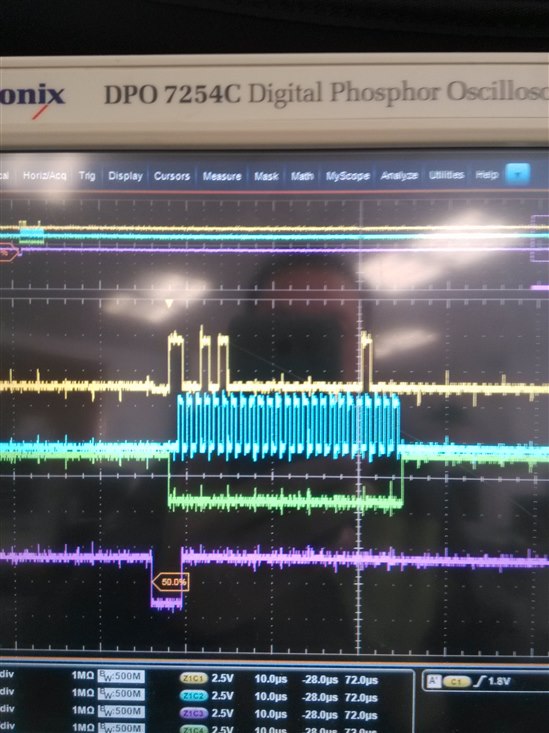

我是在每个drdy为低的时候开始读取,示波器显示结果,从上至下一次是adc的输出,sck,cs,drdy,

这样有问题吗?

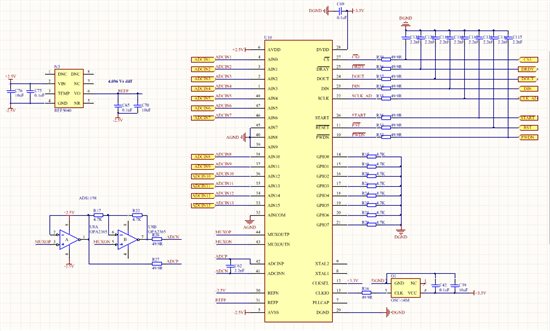

下面是原理图

这是程序

always @(posedge clk or negedge rst_n)begin if(!rst_n)begin num_reset_cmd<=8'd0; num_reg_wr<=8'd0; num_reg_rd<=8'd0; num_dat_rd<=8'd0; num_wait <=8'd0; state <=reset_spi; cs <=1'd1; flag <=2'd0; start <=1'd0; cscnt <=32'd0; rst_ad_cnt<=32'd0; init_cnt<=32'd0; flag_sclk <=1'd0; rst_ad <=1'd0; end else case(state ) reset_spi: begin //reset_spi;if(cscnt == 32'd600000)begin //cs <=1'd0; //flag_sclk<=1'd1; //rst_ad<=1'd1; state <=reset_ad;end else begin //rst_ad<=1'd0; cs <=1'd1; flag_sclk<=1'd0; cscnt <=cscnt+1'd1;end end //reset_spi reset_ad: begin //reset_spi;if(rst_ad_cnt == 32'd600000)begin//600000 //cs <=1'd0; //flag_sclk<=1'd1; //rst_ad<=1'd1; rst_ad<=1'd1; state <=reg_wr;end else begin rst_ad<=1'd0; rst_ad_cnt <=rst_ad_cnt+1'd1;end end //reset_spi reg_wr: begin // reg_wr;//cs <=1'd0;//flag_sclk<=1'd1;flag <=2'd1;//if(SCK_risingedge)begin num_reg_wr<=num_reg_wr+1'd1; case (num_reg_wr)8'd0:begin cs <=1'd0; //flag_sclk<=1'd1;end //8'd1:flag_sclk<=1'd1;//cmd for write register8'd1: begin flag_sclk<=1'd1; mosi <=1'd0;end 8'd2: mosi <=1'd1;8'd3: mosi <=1'd1;8'd4: mosi <=1'd1;8'd5: mosi <=1'd0;8'd6: mosi <=1'd0;8'd7: mosi <=1'd0;8'd8: mosi <=1'd0;//config08'd9: mosi <=1'd0;8'd10: mosi <=1'd0;8'd11: mosi <=1'd0;8'd12: mosi <=1'd1;8'd13: mosi <=1'd0;8'd14: mosi <=1'd0;8'd15: mosi <=1'd1;8'd16: mosi <=1'd0; //cmd for muxsg0/*8'd18: mosi <=1'd0;8'd19: mosi <=1'd1;8'd20: mosi <=1'd1;8'd21: mosi <=1'd0;8'd22: mosi <=1'd0;8'd23: mosi <=1'd1;8'd24: mosi <=1'd0;8'd25: mosi <=1'd0;*///config18'd17: mosi <=1'd0;8'd18: mosi <=1'd1;8'd19: mosi <=1'd0;8'd20: mosi <=1'd0;8'd21: mosi <=1'd0;8'd22: mosi <=1'd0;8'd23: mosi <=1'd0;8'd24: mosi <=1'd0;//muxsch8'd25: mosi <=1'd0;8'd26: mosi <=1'd0;8'd27: mosi <=1'd0;8'd28: mosi <=1'd0;8'd29: mosi <=1'd0;8'd30: mosi <=1'd0;8'd31: mosi <=1'd0;8'd32: mosi <=1'd0;//cmd for muxsg1/*8'd34: mosi <=1'd0;8'd35: mosi <=1'd1;8'd36: mosi <=1'd1;8'd37: mosi <=1'd0;8'd38: mosi <=1'd0;8'd39: mosi <=1'd1;8'd40: mosi <=1'd0;8'd41: mosi <=1'd1;*///muxdif8'd33: mosi <=1'd0;8'd34: mosi <=1'd0;8'd35: mosi <=1'd0;8'd36: mosi <=1'd0;8'd37: mosi <=1'd0;8'd38: mosi <=1'd0;8'd39: mosi <=1'd0;8'd40: mosi <=1'd0;//muxsg08'd41: mosi <=1'd0;8'd42: mosi <=1'd0;8'd43: mosi <=1'd0;//8'd44: mosi <=1'd0;8'd45: mosi <=1'd0;8'd46: mosi <=1'd0;8'd47: mosi <=1'd0;8'd48: mosi <=1'd0;//muxsg18'd49: mosi <=1'd0;8'd50: mosi <=1'd0;8'd51: mosi <=1'd0;//8'd52: mosi <=1'd1;8'd53: mosi <=1'd0;8'd54: mosi <=1'd0;8'd55: mosi <=1'd0;8'd56: mosi <=1'd0;//sysred8'd57: mosi <=1'd0;8'd58: mosi <=1'd0;8'd59: mosi <=1'd0;//8'd60: mosi <=1'd0;8'd61: mosi <=1'd0;8'd62: mosi <=1'd0;8'd63: mosi <=1'd0;8'd64: mosi <=1'd0;//gpioc8'd65: mosi <=1'd0;8'd66: mosi <=1'd0;8'd67: mosi <=1'd0;//8'd68: mosi <=1'd0;8'd69: mosi <=1'd0;8'd70: mosi <=1'd0;8'd71: mosi <=1'd0;8'd72: mosi <=1'd0;//gpiod8'd73: mosi <=1'd0;8'd74: mosi <=1'd0;8'd75: mosi <=1'd0;//8'd76: mosi <=1'd0;8'd77: mosi <=1'd0;8'd78: mosi <=1'd0;8'd79: mosi <=1'd0;8'd80: mosi <=1'd0;//id8'd81: mosi <=1'd1;8'd82: mosi <=1'd0;8'd83: mosi <=1'd0;//8'd84: mosi <=1'd1;8'd85: mosi <=1'd1;8'd86: mosi <=1'd0;8'd87: mosi <=1'd1;8'd88: mosi <=1'd1;8'd89: begin cs <=1'd1; flag_sclk<=1'd0; mosi<=1'd0; start <=1'd1; state <=reg_rd; end default:; endcase//end end //reg_wr; reg_rd: begin // reg_rd; if(init_cnt == 32'd5000)begin state <=wait_sck;end else begin init_cnt <=init_cnt+1'd1;end /*else if(SCK_risingedge)begin*/ /*num_reg_rd=num_reg_rd+1'd1; case (num_reg_rd)//cmd8'd0: ;//mosi <=1'd0;8'd1: ;//mosi <=1'd1;8'd2: ;//mosi <=1'd0;8'd3: ;//mosi <=1'd1;8'd4: ;//mosi <=1'd0;8'd5: ;//mosi <=1'd0;8'd6: ;//mosi <=1'd0;/*8'd7: ;//mosi <=1'd0;8'd8: ;//mosi <=1'd1;8'd9: ;//mosi <=1'd0;8'd10: ;//mosi <=1'd1;8'd11: ;//mosi <=1'd0;8'd12: ;//mosi <=1'd0;8'd13: ;//mosi <=1'd0;8'd14: ;//mosi <=1'd0;8'd15: ;//mosi <=1'd1;*//*8'd7: begin state <=wait_sck;//mosi <=1'd0;end //8'd8: state <=dat_rd; default: ; endcase*/ end //reg_rd; wait_sck: begincase(num_wait)//flag<=2'd0;8'd0:begin if(drdy==1'd0)begin//cs <=1'd0;//flag_sclk <=1'd1;//state <=dat_rd//flag<=2'd2;num_wait=num_wait+1'd1; end else num_wait<=8'd0;//state <=wait_sck;end 8'd1:begin cs <=1'd0; //flag_sclk <=1'd1; //flag<=2'd2; num_wait=num_wait+1'd1; end 8'd2:begin //flag<=2'd2; flag_sclk <=1'd1; num_wait=num_wait+1'd1; end 8'd3:begin //flag_sclk <=1'd1; //mosi<=1'd0; flag<=2'd2; num_wait=num_wait+1'd1; end 8'd4: begin //mosi<=1'd0; num_wait=num_wait+1'd1; end 8'd5: begin //mosi<=1'd1; num_wait=num_wait+1'd1; end 8'd6:begin //mosi<=1'd0; num_wait=num_wait+1'd1; end 8'd7:begin //mosi<=1'd0; num_wait=num_wait+1'd1; end 8'd8: begin //mosi<=1'd0; num_wait=num_wait+1'd1; end 8'd9: begin //mosi<=1'd0; num_wait=num_wait+1'd1; end 8'd10:begin //mosi<=1'd0; num_wait=num_wait+1'd1; //end 8'd11:num_wait=num_wait+1'd1; 8'd12:num_wait=num_wait+1'd1; 8'd13:num_wait=num_wait+1'd1; 8'd14:num_wait=num_wait+1'd1; 8'd15:num_wait=num_wait+1'd1; 8'd16:num_wait=num_wait+1'd1; 8'd17:num_wait=num_wait+1'd1; 8'd18:num_wait=num_wait+1'd1; 8'd19:num_wait=num_wait+1'd1; 8'd20:num_wait=num_wait+1'd1; 8'd21:num_wait=num_wait+1'd1; 8'd22:num_wait=num_wait+1'd1; 8'd23:num_wait=num_wait+1'd1; 8'd24:num_wait=num_wait+1'd1; 8'd25:num_wait=num_wait+1'd1; 8'd26:num_wait=num_wait+1'd1; /*8'd26:num_wait=num_wait+1'd1; 8'd27:num_wait=num_wait+1'd1; 8'd28:num_wait=num_wait+1'd1; 8'd29:num_wait=num_wait+1'd1; 8'd30:num_wait=num_wait+1'd1; 8'd31:num_wait=num_wait+1'd1; 8'd32:num_wait=num_wait+1'd1; 8'd33:num_wait=num_wait+1'd1;*/8'd27:begin cs<=1'd1; flag_sclk<=1'd0; num_wait<=8'd0; flag<=2'd0;end endcase end

你好,我遇到一个问题

发现CLKIO无输出,晶振工作正常,看了手册,默认是用了外部晶振的话就会在CLKIO口的引脚输出,可是用示波器测不到

是我的芯片没有正常工作吗?

求指出问题