ads1292R的SPI时序问题

新手想请教

我利用MSP430F5529控制ADS1292R,使它在连续转换数据的模式下运行,

但时序看起来似乎有问题,想请有经验的人指点我一下。

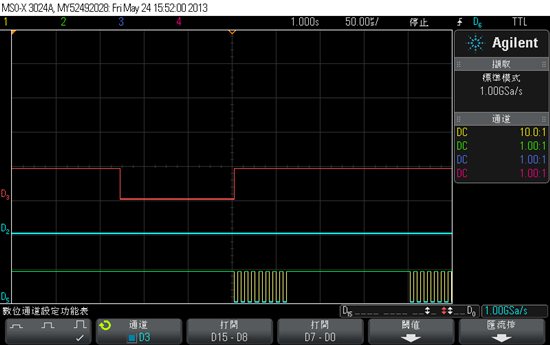

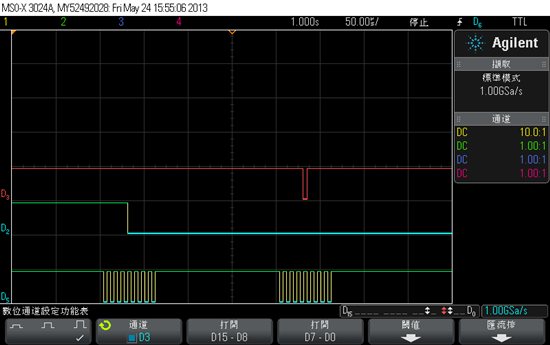

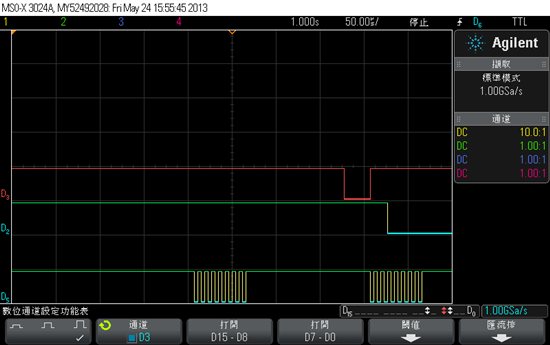

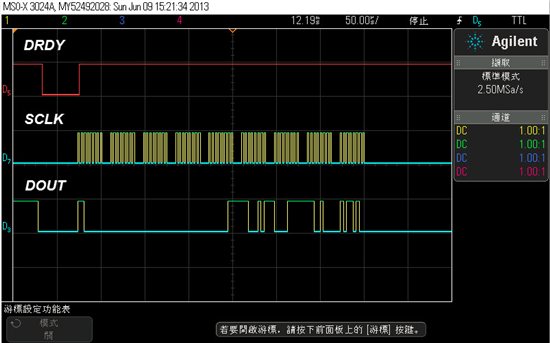

下面是示波器的截图,第一条(红线)是DRDY讯号,第三条(绿色)是SCLK讯号。

据我看数据的时序图,在连续转换的资料模式时时序都是很规则的,

但在我的截图中可以看到,DRDY的宽度是变化的,甚至在SCLK有讯号时,

DRDY还产生trigger,想请教是出了什麽问题,谢谢!

Hi

DRDY是数据转换完成与输出提示符,当它置低后会在DOUT第一位的SCLK的下降沿回复高状态。

也就是说并没有固定的DRDY低电平时间定义。

注意此时的必须有正常的SCLK(因为要下降沿DRDY才跳变), 而在这二个过程中DIN保持低。

谢谢Johnsin Tao的回覆。

我有一些疑问如下 :

1.据我看的理解,当资料转换处于连续模式时,

DRDY应该是以固定的周期做高低电平交换DRDY Should Toggle at fCLK),

这里是我理解错误吗

2.在我贴的三张图中,第一与第三张的DRDY确实是在SCLK的第一个下降沿转换电平,

但如第二张图,我的DRDY常会在SCLK中有很短暂的低电平表现,想请教这是什麽问题。

谢谢!

Hi

是的,作为一个稳定的连续转换,DRDY是固定周期出现的,并且DRDY置低的时间是固定的。

这个就要检查从DRDY开始置低到第一个SCLK下降沿的时间中是否有不固定的因数存在,例如SPI口的配置,从CS置低开始有SCLK输出, 这其中的时间控制是否固定。

DRDY常会在SCLK中有很短暂的低电平表现, 需要检查一下转换设置,是否有其他的控制影响到DRDY, 例如在这个过程中DIN一直处在低,或者其他的接口信号出现变动影响到ADC的正常转换。

目前读回command的值是对的,表示命令有写进去。

但我的DRDY仍不是週期方波,且下降沿出现的位置也不正确(如首贴文的图所示)。

我的程式是照datasheet p.63的程序所写的,不晓得哪裡出错了 :

int main(void) {

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

unsigned char dat[3];

// CLK setting

UCSCTL3 |= SELREF_2; // Set DCO FLL Reference = REFO

UCSCTL4 |= SELA_2; // Set ACLK = REFO

__bis_SR_register(SCG0); // Disable the FLL Control Loop

UCSCTL0 = 0x0000; // Will be Set Automatically by FLL

UCSCTL1 = DCORSEL_2; // 1 MHz range

UCSCTL2 = FLLD_1 + 32; // Set FLL to approximately 1 MHz:

// FLL divider result = 32768

// 64 * 32768 = "2 MHz"

// set related pins with ADS1292R

P2DIR |= BIT3; // P2.3 -> CLK_SEL

P8DIR |= BIT0 + BIT1 + BIT2; // P8.0 -> RESET, P8.1 -> START, P8.2 -> CS'

// SPI initialization

P3SEL = BIT0|BIT1|BIT2; // Set Pin Function for SPI Mode

UCB0CTL1 |= UCSWRST; // **Put state machine in reset**

UCB0CTL0 |= UCMST+UCSYNC+UCCKPL+UCCKPH+UCMSB; // 3-pin, 8-bit SPI master

// Clock polarity high, MSB

UCB0CTL1 |= UCSSEL_2; // SMCLK

UCB0BR0 = 0x02; // /2

UCB0BR1 = 0; //

UCB0MCTL = 0; // No modulation

UCB0CTL1 &= ~UCSWRST; // **Initialize USCI state machine**

// indicate ADS1292R use internal clock

P2OUT = BIT3; // indicate ADS1292R use internal clock

__delay_cycles(100); // wait for oscillator to wake up

// wait for 1s for ADS1292R's power-on reset

P8OUT |= BIT0; // set RESET'=1

delay_ms(1000); // wait for 1s for power-on reset

// reset ADS1292R & CS' pin tied low

P8OUT &= ~BIT0; // issue reset pulse

delay_ms(100); // wait 0.1s

P8OUT |= BIT0; // clear reset

P8OUT &= ~BIT2; // CS' tied permanently low

// send command

Send_CMD(0x11); // sent SDATAC command

dat[0]=0xA0; // CONFIG2 = A0;

Send_CMD_Multi(0x40+0x02, 1, dat); // Config. CONFIG2 = 0xA0 to use internal reference

dat[0]=0x2C; // RLDSENS = 2C;

Send_CMD_Multi(0x40+0x06, 1, dat); // right leg drive

dat[0]=0xC2; // RESP1 = C2;

Send_CMD_Multi(0x40+0x09, 1, dat); // turn on RESP demodulation&modulation

// DRDY' interrupt

P1IE |= BIT0; // P1.0 interrupt enabled

P1IES |= BIT0; // P1.0 Hi/lo edge

P1IFG &= ~BIT0; // P1.0 IFG cleared

// START = 1

P8OUT |= BIT1; // START = 1

// send continue mode command

Send_CMD(0x10); // enter the continue mode

__bis_SR_register(LPM0_bits + GIE); // CPU off, enable interrupts

return 0;

}

调试很久还是没成功,希望有人可以指点一下,谢谢!

Hi

建议通过从时序上确认错误,在修正程序,在datasheet:http://www.ti.com.cn/cn/lit/ds/symlink/ads1298.pdf

在datasheet中有很多参考时序都是可以参考的。

hi, Johnsin Tao

谢谢你的建议,目前我的时序已经正确了。

不过接收到的值却是错误的,

我用电源供应器从INP和INN输入0.5V的直流电压,

经PGA(*6)放大后应该是3V,超过参考电压的2.42V

所以输出应该是7FFFFF,但从示波器上看到的值却不是这样的,

想请问该从哪裡debug?

谢谢~!

Hi

你在示波器上看到的值是多少?

Hi

上述指的是数字输出。

Hi

芯片Power on 后reset一下,然后在写相关配置。(很多寄存器配置采用默认设置就可以了, 此时PGA=6, Vref=2.42.)

SPI的时序参考datasheet:http://www.ti.com.cn/cn/lit/ds/symlink/ads1292.pdf 第十页。

hi,Johnsin Tao

我在power on时有作reset的动作。

今天再测试一次,却发现DUOT没有讯号了,

检查ads1292r的CLK output(pin 17)也没有clock,

是否是ic损坏的状况?

不过DRDY与SLCK的时序依然正常

Hi

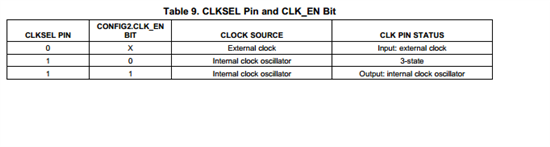

CLK 配置如下:

如果你是采用内部CLK, 并设置CLK_EN=1, 正常供电,就有CLK输出。

CLK_EN的默认设置是0,也就是没有CLK输出,所以没有CLK并不意味着芯片损坏了。

Hi

上述,如果你采用外部CLK, 也就是说你的MCU必须要有CLK输入到ADS1298.

另外确认一下powerpup的时序, 见datasheet: http://www.ti.com.cn/cn/lit/ds/symlink/ads1292.pdf 第六十二页 figure 62.

Hi

事实上,你可以按照datasheet 第63页的步骤来做一个测试,主要是参考他的步骤,也就是你确认你整体的时序。

Hi, Johnsin Tao

谢谢你的回覆。

事实上我的设计就是参照p.63的程序,

经过一天的测试有一些疑问如下,想请教你 :

目前在无输入的状态下,ECG和呼吸仍有不小的值,如下示波器截图。

同时我量测PGA输出,大约有1.x伏的直流,据我理解,类比讯号经PGA

放大后就会经过ADC转换成数位讯号,所以我在示波器看到输出值不如

预期是0(或是很小)其实是正常的,即是上述的直流本身。

另外我量测ADS1292RECG-FE开发板上的DOUT讯号,在无输入讯号的

情况下完全为0(包括状态位元组),这是正常的吗?

Hi

在做测试时,不要无输入,可以接GND(外接,或者内部设置都可以), 此时ADC如果有非常非常小的数字输出是正常的。

EVM当数字输出为0时,最好还要还要加一个小电压测试一下,判定ADS1292是有在转换。

Hi

打扰下,我最近也在做MSP430F5529与AD1292通讯的,时序那边一直没通过,软件仿真时序可以读值,但是真正用时钟的时候不行,不知道你的成功了吗?能不能指教一下,我有几个问题:

1:MSP430与AD1292 SPI通讯的时候是不是对时钟严格,我的CLK是1M,SCLK是512K(1/2),不知道这样可否。

2:通讯SCLK对信号的相位那些有要求吗?即UCCKPH 与UCCKPL需要设置吗

3:是否需要用SPI中断去读取数据

谢谢

您好,看到你回复的帖子,相比您应该对ADS1292r特别了解,我现在的问题是内部晶振可以正常起振,寄存器可读可写,就是连续模式的时候,DRDY和SCLK的时序不对,DRDY也是在SCLK的第一个下降沿变化,但是每次只能发送状态位的前八位,然后DRDY就拉低,因此发回来的数据就是C0,C0,C0,全是C0。希望能够得到您的帮助。

你好!我的读到的数据也是C0,C0,C0,.........不知道是怎么回事。

Hi Ray Hsu

虽然你的帖子已经很久,但是还是想想你请教。

我现在用的ADS1291,复位后,对寄存器的读写操作,DOUT一直都没有数据出来。

但是我通过IO口启动转换,DRDY却有定时的脉冲输出。

我看到你在前面也提到过DOUT没有数据,请问你是如何解决的?程序上应该注意哪些问题呢?(我已经安装Datasheet的时序及流程去初始化了,一直不行呢)