ADS826模数转换器布局布线PCB设计

时间:10-02

整理:3721RD

点击:

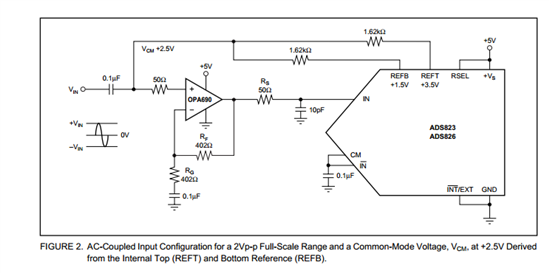

按照ADS826芯片手册给出的参考设计,设计出来的ADS826采样电路,不能正常工作,OPA690放大器输入端是一个500mv左右的15MHz的正弦震荡信号,AD的时钟是由FPGA提供的,当不给AD时钟时放大器OPA690能够正常放大,当用FPGA给AD提供60MHz的时钟,就会有很大噪声,采集的数据也都是噪声,怎么解决?有没有推荐的ADS

826采集电路的PCB布局布线?(附件中是参考芯片手册,所设计的电路)

826采集电路的PCB布局布线?(附件中是参考芯片手册,所设计的电路)

那可能是布线的问题,给AD提供60MHz的时钟, 这个时钟信号给电路带来了很大的数字噪声,这条时钟线要好好地处理了

那这条时钟线要怎么处理呢?我可不可以加个您的qq