ADC的时钟线一直为高电平

时间:10-02

整理:3721RD

点击:

大家好,最近在用MSP430F5529调试AD7688的ADC,遇到的问题是AD7688的时钟线一直处于高电平状态,导致无法发送数据,请问可能有哪些原因造成的,谢谢。

这个clock是外部给的,按你的意思是MCU没法把它拉低吗?

ad7688是我们家的料号吗?感觉像友商的产品

你的意思是用430产生时钟供给7688吗

AD7688是ADI的ADC产品,不是TI的呢。

可以看看TI 的ADS8861。管脚兼容。

AD7688 的时钟应该是MSP430给过来的。同时要注意两边逻辑的电压。

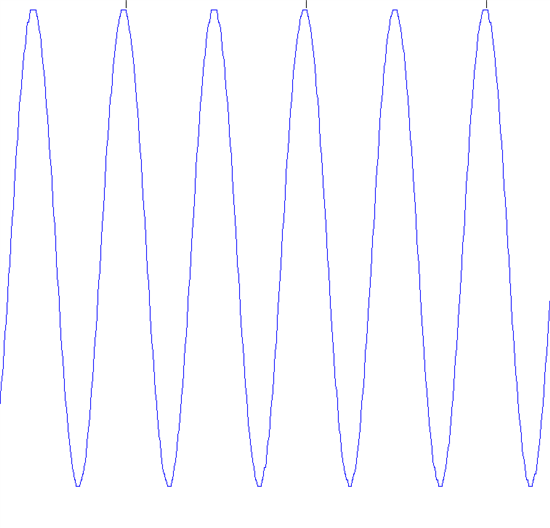

恩恩,现在这个问题解决了,但是采集的信号没有峰值,如下图所示:

在峰值处都会有饱和的现象,请问可能的原因是什么?谢谢。

感谢回复,市中心不能拉低是因为我的配置除了问题,现在可以采集到数据,但是峰值处总是采不到,为什么呢?

降低信号的幅度

增加clk的频率,加大采样率

降低输入信号的频率

还是有问题啊,请问贵公司的ADS8861有没有参考的代码呢

你好,你所说的是否读写的接口代码,其实比较简单参照6~7页相关时序即可,也可以申请TI评估板测试。