24bit,ADS1259技术手册中描述的spi通信时钟配置疑问

时间:10-02

整理:3721RD

点击:

最近正在做以ADS1259为ADC的项目,涉及到spi时钟tsclk的配置时,datasheet中的一些描述让我有些迷惑,望得到TI工程师的解答。

先声明下DS里面的两个参数tsclk--spi时钟,tclk--ADS1259时钟(DS给的参考是7.3728MHz,此时钟由外部晶振或内部时钟提供均可)。

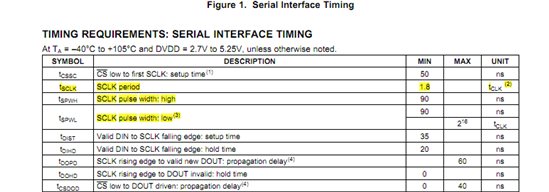

DS第6页给出了下表

其中tsclk需要满足,tsclk>1.8tclk。

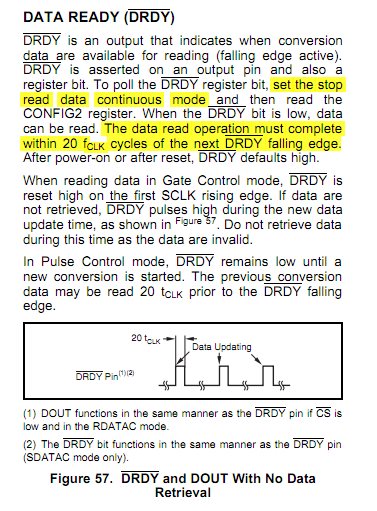

同样,在DS第28页在对DRDY信号描述中,阐述“转换好的数据必须在DRDY下降沿到来之前的20个tclk内被主设备取走”,并给出图示figure57,

从ADS1259读操作过程,无论对于连续转换模式,还是单次转换模式,如果不设置奇偶校验功能,读出一个转换结果至少需要24个spi时钟周期tsclk,于是就有24tsclk<20tclk,即得出tsclk<0.83tclk,对于这个结论岂不是同DS第6页给出的tsclk>1.8tclk自相矛盾吗?

望尽快得到解答!

我看这里是断章取义了.

整体的意思, 说是在 DRDY 低电平的时候, 可以读取数据, 并在下一个下降沿之前完成读取.

可是DS中很明确的提出了20tclk这个概念,还是想搞清楚“数据读取,20tclk和DRDY下降沿”这三者是什么关系!

这样理解不知道是否正确:数据读取需要比DRDY下降沿到来早20个tclk完成,因为对于ADS1259,DRDY下降沿之前的20个tclk是data update time。