关于SN65LVDS32输入悬空的疑惑

时间:10-02

整理:3721RD

点击:

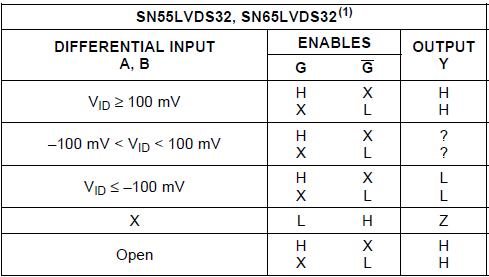

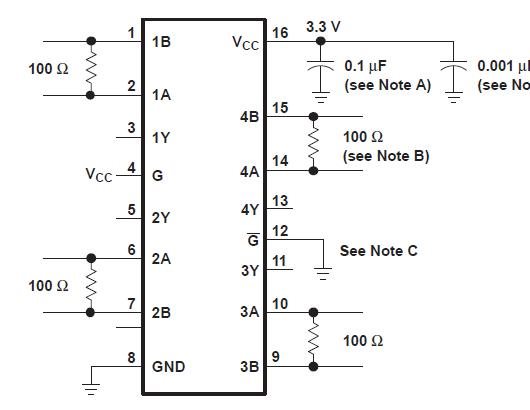

SN65LVDS32是差分转单端的接收芯片,根据datasheet的描述,当–100 mV< VID < 100 mV时,不管G、G/为何状态,在输出端总会有不确定的数据输出,在datasheet的典型应用中,A、B之间连了一个100欧姆的电阻,那么当上电时,VID应该就在上述的那个范围内,那么输出端就会有不确定的数据输出,当输出接到MCU时,这个数据就会被采到,那么这个数据怎么处理呢?是不是需要在AB做上下拉来保证悬空时的输出状态呢?新手问题,希望大神解惑,谢谢!

图一、真值表

图二、典型应用

这个是把大于100mV的信号判决为高,把小于-100mV的信号判决为低。中间电平是不定态

谢谢您的回复。你说的我知道,我的意思是中间电平的时候输出是不定态,但是也会有输出,那么MCU就是采到相应的数据,那么我们该怎么去处理这些采集到的数据呢?或者说通过一定的手段让他没有输出吗?

SN65LVDS32内部集成了open-circuit fail-safe保护电路,这在datasheet Page18详细介绍了你说的这种情况,即如果输入端悬空或者差分输入电压在-100mV~100mV之间时SN65LVDS32是如何处理的,你可以先阅读下,如有问题可继续讨论。

感谢您的回答。