DAC5574的使用问题

您好,我在使用DAC5574时碰到了如下问题:

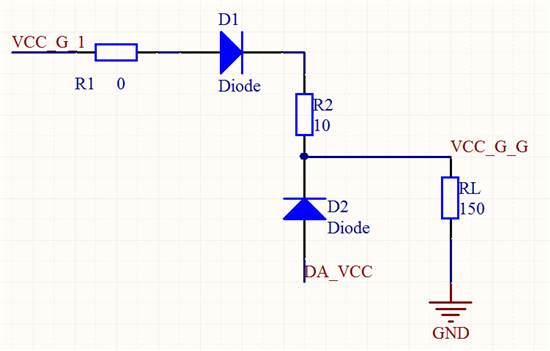

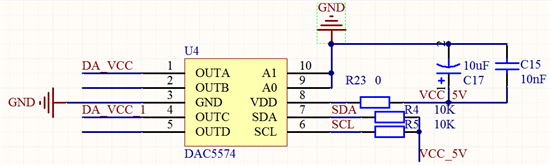

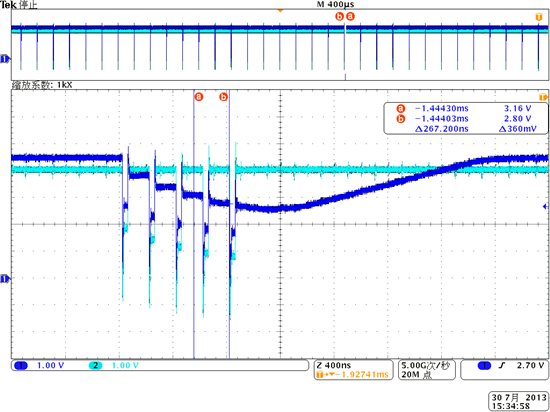

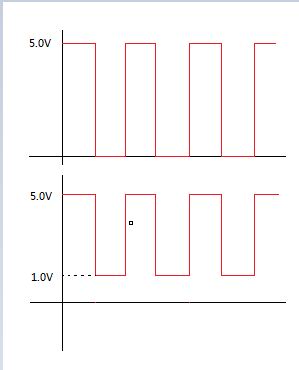

使用DAC5574给D2二极管的正向输入端供给一个恒定的电压,电压幅值从1V调整到5V,VCC_G_1是电路的输入端,使用FPGA产生500MHz,振幅为0V~ 5.0V的矩形波信号输入,RL为恒定的负载150Ω,RL上需求的最小电流为30mA,测得的信号时下图所示。

蓝色线为DA_VCC,为什么不是一个恒定的电压值?绿色部分为VCC_G_G的输出信号,因为DA_VCC的下端不断在降低,这样造成了输出信号的低端也在降低,这个是不能接受的。请问这个是什么原因造成的?

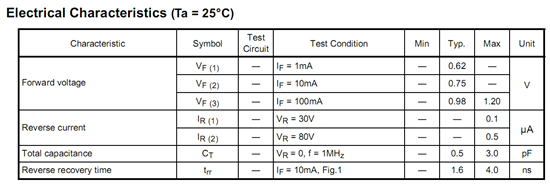

另外,我使用的二极管为TOSHIBA的1SS352,电气特性也在下图中。

没看明白这是什么应用,似乎仅仅是想在负载上得到一个方波电压?

出现这样的情况挺正常吧,FPGA输出没有什么驱动能力,二极管导通时是个低阻,和R2,RL串在一起,阻值也很低,一般的FPGA输出管脚应该驱动不了这么小的负载。另外,那个二极管电压从0到1,从1到0需要一个时间启动和恢复吧,可能这就是那些尖峰的来源。

谢谢您的回复。

下图就是我想要的应用,把方波信号的低电平抬起来,具体抬到多少的电压,由我使用DAC的输出决定。使用上面的二极管电路在理论上可以达到效果。另外二极管的trr只有1.6ns,这个够用了。

我的疑问是为什么DAC输出的电压会随着输入的电平变化而发生变化,并且还有一个先下降再上升的过程(蓝色的线)?

即使二极管导通后正向电阻很小,但是反向电阻很大呀,而且二极管的输入端是由DAC供电的,这个电压一直是一个恒定的值,并不是0V,跟RL没有构成并联,也就不会存在并联电阻很小的说法。

DAC5574手册第3页,短路电流在5V供电下50mA,现在的应用里,假设二极管导通电阻极小,则电阻从DAC抽出的电流是5V/(10+150)=33mA,已经很接近短路电流,此时DAC的输出电压很可能会降低,因为无法维持如此大的输出电流。

二极管的模型应该不仅仅是一个低阻/高阻,应该还有一个等效的并联电容。这样一个电容,在DAC输出高时充电,输出低时放电,在充放电的瞬间,会有很大的尖峰脉冲。同时DAC本身在做切换时,也会有跳变产生的脉冲。降低脉冲的方法是加电容,以吸收这部分脉冲能量。

我觉得没必要用二极管这种器件,你的应用,最直接的解决办法是DAC后接运放做buffer,找一个驱动能力比较强,足以驱动150欧姆电阻的运放就可以了。

谢谢回复。

我为什么使用二极管,这是因为我的输入信号的频率很高,大约是在500MHz左右,运算放大器我也找过,并且实际的测试过,slew rate等参数没有我想要的那么高,比如,我输入的信号上升时间大约是2ns左右,即2ns内从0V上升到3.3V,运放构成的加法电路根本达不到要求。所以我才选择使用二极管抬高低电平,但是这种方法必然会带来驱动能力的问题。

我现在的做法是打算在DAC与二极管之间加入一个驱动能力比较高的运放组成跟随器,这样可以保证输出电流能满足我的需求。接下来再继续改进。

那最后请问您,如果我不适用二极管,还有什么比较好的方案可以抬高低电平?而能满足500MHz的信号以及不改变上升时间以及下降时间呢?

哦,单独在DAC和电阻之间加运放,改善应该不大。FPGA的输出口应该支持不了最大33mA的输出电流(5/160),运放应该是在FPGA后面加。

2ns内从0到3.3,摆率就是1650V/us,TI的高速运放可以支持到这么高的摆率的,你可以评估一下THS4508/4509/4511/4513。