常被忽略的那80%重点,SAR-ADC 电压基准电路 part II

上文part1详细分析了为什么SAR-ADC的电压基准电路设计是设计重点的80%。下面我们就开始设计一个高质量的电压基准。虽然TI的相关英文应用手册对这部分有分析,我还是想详细的一步一步的分析一下这个过程,以便尽量让大家看的更清楚。

(1) 基准源的Trim引脚加退耦电容。

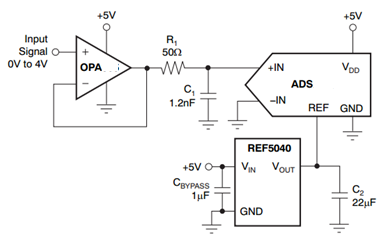

这一点被很多的工程师所忽略。可能是看到基准源的datasheet的应用电路中(如下图是REF50XX系列的datasheet),没有加电容,就参照上面的电路设计了。

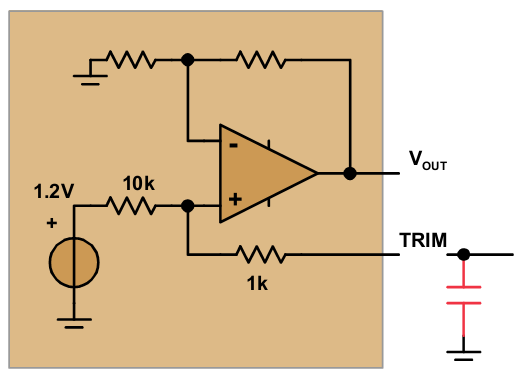

让我们再进一步的看一下REF50XX系列bandgap基准源的内部,如下图,芯片内部有一个1.2V的带隙基准,和一个用于设置精确输出电压的放大器。这两个就是基准噪声的主要来源。并且带隙基准的噪声还要经过后面的放大电路再放大一次。

根据噪声系数(NF)理论,最前级的噪声往往决定信号链路的噪声。因此越在前级减少噪声越有效。如果我们在Trim引脚加一个电容,它将与内部的1K欧电阻形成一个低通滤波器。它将给 bandgap增加一个14.5Hz的极点和160Hz的零点。如果想进一步降低带宽可以加更大的电容。这里即使加一个1uF的电容到trim引脚,都会使总的输出RMS噪声减小2.5倍,2.5倍啊。多么超值的一个电容。上面用理论分析了这个电容的作用,还是缺乏些说服力。下面是TI的工程师的测试数据,由测试结果可见在Trim引脚加了电容的基准源输出噪声大大的降低了。因此这个电容,是非常超值的。

(2) 基准源输出端选用大电容,最好是ESR大的电容

开篇图中的10uF电容是用来储存足够多的电荷,以备ADC内部转化电容抽取时,保证基准源电压的稳定。有些工程师可能会知道,SAR-ADC内部的采样电容和转化电容的值一般为几十个pF。10uF的电容储存的电量给几十个pF提供电荷简直是小菜一碟。大家要知道,对于16bits的ADC,如查基准有15ppm(百万分之十五)的波动,就是一个LSB。因此要保证输送给内部转化电容充分电荷时,基准电压的稳定,就要使用大的电容。所以这个电容推荐值都是在uF级(一般选10uF)。现在明白了,这个电容,不单单是给基准源滤波,它肩负着更重要的使命,为ADC的转化电容输送电荷。

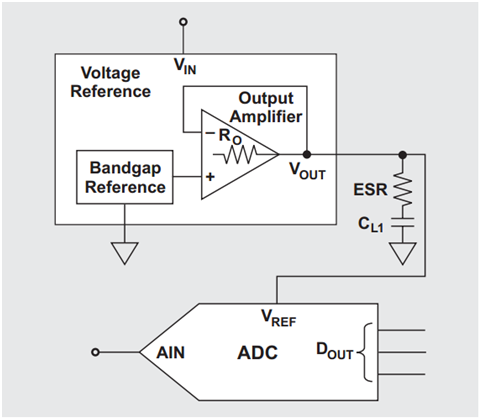

这个电容的选取又会引出一个新问题,我们该选ESR小的瓷片电容(ESR约为0.1欧),还是ESR大的钽电容(ESR约为1.5欧)。照经验来说,电容的ESR越小越好。但对于基准源的输出端电容,可不是这样的。我们再看一眼基准源的内部结构,就可以看出,这个电容是作为基准源内部buffer放大器的负载而接到输出端的。运放的输出端接大电容,好像不太保险,是的,这会引起运放的不稳定。因为它与运放的输出电阻形成一个新的极点,这个极点频率会很低。因此这一点应该选择ESR大的电容,构成电路如下图,这个ESR会对电路进行滞后补偿。

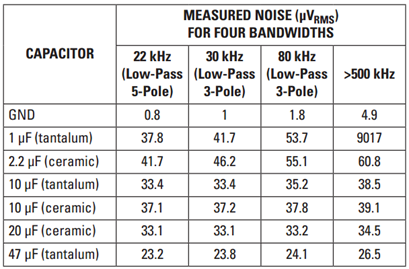

实际的测试结果也表明,使用大的ESR的钽电容基准源输出端的电容时,基准源的噪声确实会下降一些,如下表所示。在实际的电路中由于成本的原因,也可以选用瓷片电容,只要在瓷片电容与基准源输出端串一个小的电阻来提高ESR就可以达到同样的效果。

以上的基准源,就可以用在14位的ADC中了。

回part I

常被忽略的那80%重点,SAR-ADC 电压基准电路【TI FAE分享】

下一小节part III

常被忽略的那80%重点,SAR-ADC 电压基准电路 part III

10uf的钽电容跟10uf的瓷片电容滤波效果有时候是不是差别很大?

因为我上次做一个ldo发现在其它条件都相同的情况下,输出都是加10uf大小的电容,钽电容很稳定,瓷片电容输出却有100多mv的锯齿波,是不是esr的影响啊?