常被忽略的那80%重点,SAR-ADC 电压基准电路 part III

上文part II,分析了基准源电路提高性能的两个方面。如果要进一步提高基准源的性能,需要在以下几个方面入手了。

(1) 为基准源的输出端加低通滤波器

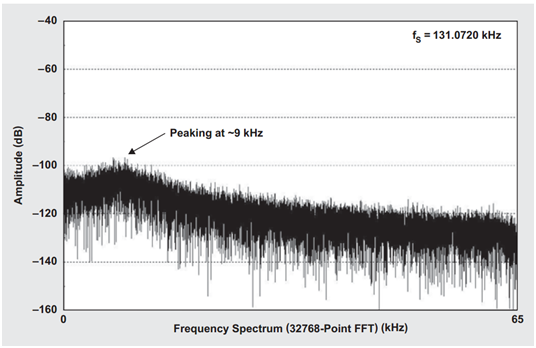

上一小节中,C2作为内部buffer的电容负载,虽然选择ESR大的电容,但它还是会引入一个极点。这就有可能使buffer输出端的噪声增加。如下图,在大约9KHz的有一个peaking。这个peaking成了基准源输出噪声的主要部分。文献中在80KHz带宽内测量的RMS值大约为16.5uV。如果这个基准接到ADC中,在65KHz步率范围内的peak-peak值约为138uV。这就是这个基准电源适合于8-14bits的ADC的原因。

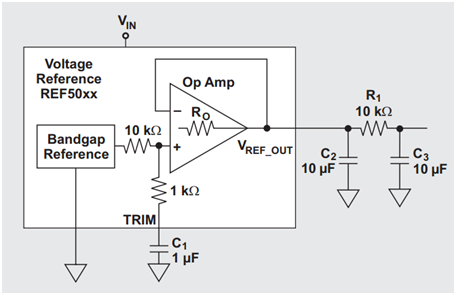

由于电容C2造成的buffer不稳定而引起的噪声增加,可以用一个低通滤波器有效的滤除。滤波器的R1为10K欧,电容C3为10uF,如下图,这个电低通滤波器的带宽约为1.59Hz,这个够低了吧。

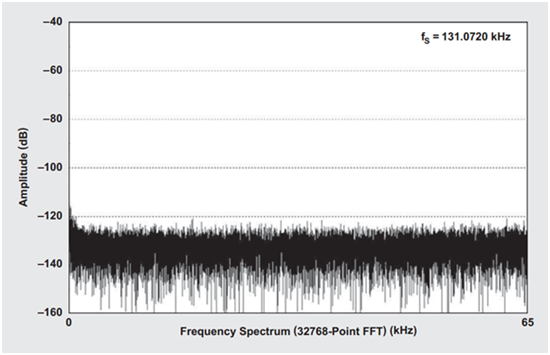

下图是加了低通滤波器后的基准源噪底。对比前后发现这个低通滤波器的效果很明显。此时的基准源噪声RMS值为2.2uV,peak-peak值为15uV。

(2) 为基准源输出增加buffer

上面加了R1=10K,C3=10uF低通滤波器的电路,是不能直接连接到SAR-ADC基准源输入端的。原因就是,如果C3上的电荷被ADC的基准源电路抽走了,基准源要为C3充电,而R1,C3构成的RC电路的时间常数为=0.63S。因此给C3充电是一个非常慢长的过程。这就会造成C3电荷得不到及时补充。而失C3上的电压出现下降。这就要引出另一个关键器件,基准源的buffer。需要选用一个运放加在基准备源滤波电路后面做外部的buffer。

这个buffer的选择是很有讲究的,因为它不只是增大基准源的驱动电流。它的更重要的使命是快速的给驱动电容充电。当10uF驱动电容的电荷被ADC抽走时,势必造成电容的正端的电压微小下降。这时就会引起buffer运放的输出电压下降。这就会引起运放的反馈系统的响应,使输出电压回到原来的值,也就是等于Vref的值。回到原来的值的过程受限于两个因素:(1)一个是运放的能否快速反馈调整输出电压回到原值,这就需要一个宽带宽、高响应速率的运放做buffer,而且还需要高精度。这也就是为什么TI的SAR-ADC的参考设计中基准源的buffer,一般都会选用OPA350的原因。OPA350的增益带宽积GBW为38MHz,而输入失调电压典型值为±150uV。千万别觉得它做基准源的Buffer是大材小用。正因为它有这样高的指标和能力,才用它担任电压基准buffer的这一重任。(2)运放能够有足够的驱动能力,快速给后面的电容充电,这个要求一般容易达到。

回part I

常被忽略的那80%重点,SAR-ADC 电压基准电路【TI FAE分享】

下一小节part IV

常被忽略的那80%重点,SAR-ADC 电压基准电路 part IV 最后的关键

opa211做buffer怎么样?