ads8556硬件设计问题

时间:10-02

整理:3721RD

点击:

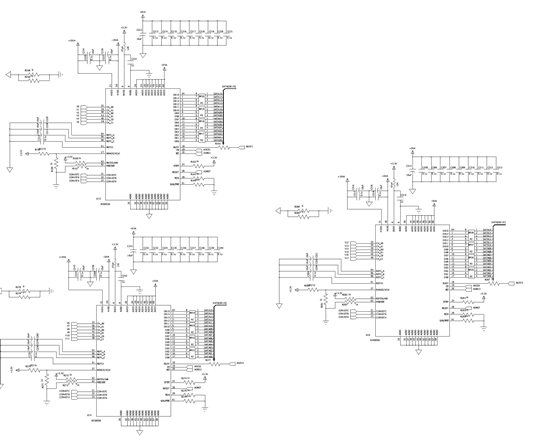

我的板子上3片ADS8556采用的是16bit并行数据总线与FPGA相连。我把3片的16位总线全部并联了,电路图如下:

看不清请见pdf附件。

唯一问题就是3片的16位总线直接黏在一起可以吗?

我现在调板子,2片ADC同时工作,分时读取数据没有问题;但当3片同时工作,FPGA内部就乱套了,当摘除16位总线上(我在每片ADC的16bit总线上串联了33欧的排阻)排阻后,FPGA就正常了。

我不知道直接这么连接总线会不会有问题?没有查到参考资料说不允许这么连或者允许这么连。请问专家,这样做可不可以?

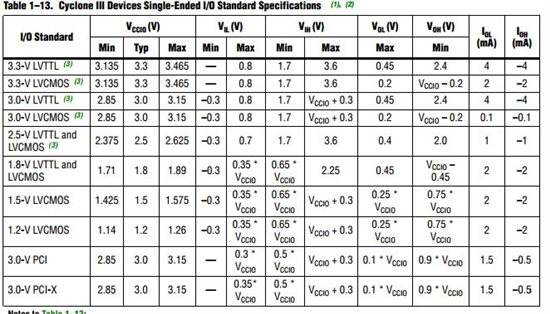

有没有FPGA的I/O输入参数? 这应该是和ADC并行输出端口以及FPGA的输入参数有关。

把33Ω的电阻换成0Ω试试,像这种接法,一般在每个ADC的输出端加一个带3态输出的buffer应该更好。

使用的3.3v LVTTL标准。ADS8556的16bit总线不是3态的嘛,是双向的。由rd信号控制输出,不知道出的是什么问题,我用示波器测波形,很好的,没严重的畸变现象,不知道我这样连可不可以?为什么把33欧改0欧呢?我的FPGA内部时序全部错乱,去掉排阻后,这样信号就进不了FPGA,FPGA内部就正常了。不知为什么

你测量的位置是FPGA的引脚,还是总线上?如果可能,测一下,FPGA相对应的引脚上的信号质量。

ADS8556是可以挂在总线上使用的。我们有客户就是将三片ADS8556挂在TMS320F28335总线上使用的。请你先确定一下,在读其中一片ADS8556时,其余的两片的CS信号是否都置高电平。然后测量一下输入到FPGA引脚上的信号的质量。