信号放大电路中的输入、输出阻抗是怎么定义的

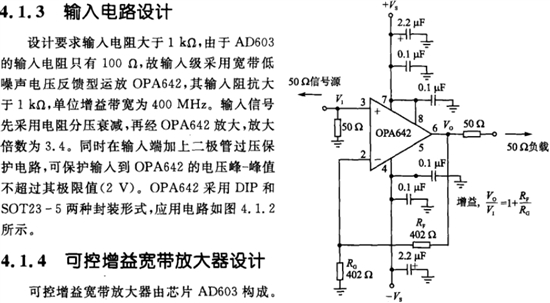

我要设计的是一个宽带放大器(电赛2003B题),题目中要求输入阻抗≥1KΩ,那么这里所说的1K是怎样一个概念,就是说是指哪里的阻抗,怎样测得的?我理解为用万用表直接接到电路的信号输入端所得到的阻抗值,这样理解对吗?如果是这样的,请看图片,图片是前置阻抗匹配电路,这样按照我所理解的测试方法测得的阻抗必然≤50Ω,这应该如何解释呢?图中输入端的50Ω电阻是为了和信号源的50Ω内阻相匹配的。

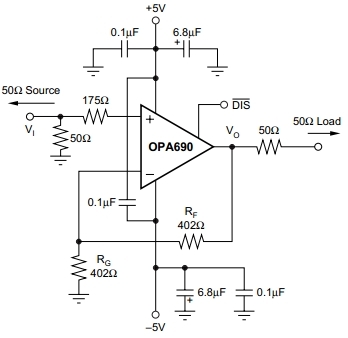

另外,为了给正向输入端提供了一个基础输入偏置电流,以消除与反相输入端相匹配的200Ω(402||402)阻抗,我还有没有必要在正向输入端与50Ω的节点后串联一个175Ω的电阻呢?正如opa690手册中给出的应用电路,如右图所示

还有一个关于输出阻抗的问题,正如第一张图所示,如果下一级接输入阻抗为100Ω的ad603进行进一步放大时那么我的第一张图中输出时是否要将50Ω的匹配电阻换成100Ω,或者在下一级运放的输入端将阻抗匹配成50Ω?

恳请高人指点一二,在下感激不尽。

你好,

这样设计的前级电路阻抗匹配得到的输入阻抗很明显是50欧姆左右,不可能大一1k。

因为通向放大电路的输入阻抗就是运放的输入阻抗,该阻抗与50欧姆并联,就会得到比50欧姆小接近50欧姆的阻抗,与信号源50欧姆进行匹配,根本达不到1k以上的输入阻抗。

您好,

感谢您的回答,看来我对输入阻抗测量的理解是正确的吧?按照您的分析就会有一个矛盾,要是我进行阻抗匹配就肯定达不到要求(输入阻抗≥1kΩ),如果我不进行阻抗匹配(把50Ω的电阻去掉)就不合手册上的参考电路,我该怎样取舍呢?

我测试过,如果把正向输入端的50Ω电阻去掉对电路没有太大的影响,这样看来50Ω的匹配电阻到底有什么作用呢,作用又有多大呢?

虽然我也不是很明白,不过可以看看这篇文章,或许有点帮助。http://www.dz863.com/all-technology/Electronics-Glossary/Smith-circuits.htm

谢谢你。我又对阻抗匹配多了一些认识

我突然想到一个问题,就是在宽带放大器中多级级联时的级与级之间通常不做阻抗匹配,是不是由于用了电容进行交流耦合的缘故呢

下一级的输入阻抗就是上一级的输出阻抗,测试上一级的输出阻抗可以在输出端串联一个电阻,有电阻分压比来确定输出阻抗。

参考一下,不对请指教。

"题目中要求输入阻抗≥1KΩ",是单纯指的运放的输入阻抗,此时不应该将并联的50欧姆考虑在内。你并联50欧姆电阻是为了更好地实现信号的传输,与前面信号源的阻抗相匹配。换个角度思考一下,如果你运放的输入阻抗≥1KΩ,与50欧姆阻抗并联得到的阻抗值很接近50欧姆,然而若输入阻抗值不是很大,这时再与50欧姆阻抗并联就不是很接近50欧姆,也就会影响到信号传输的质量。

运放级联时,前级输出阻抗很小,后级尽量用同相放大器,这样后级输入阻抗非常大,这时两级间不需要阻抗匹配了吧,

我觉得加50欧阻抗匹配,只是用在测试时与函数发生器和示波器匹配,不知道对不对,希望大家指点下。

还有就是示波器表笔负载和示波器负载都上兆欧,为什么要串联50欧电阻啊

这样看来我的担心是多余的咯,那就没有矛盾了,我就可以安心地加上匹配电阻了

串联怎么来分压和确定输出阻抗

一般相同芯片级联之间不需要匹配,与不同芯片连接时要做匹配