关于高速运放输入阻抗和输出的“阻抗匹配”问题

时间:10-02

整理:3721RD

点击:

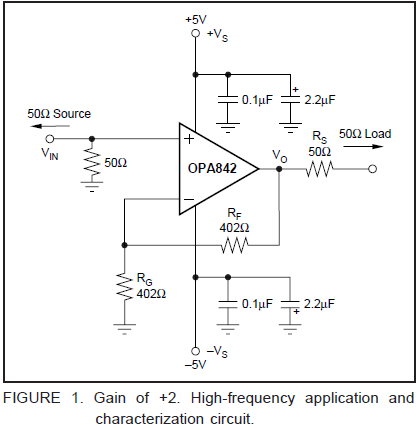

这是opa842手册的一个放大电路。opa842放大器的输入端接个50欧姆电阻到地,此时源阻抗50欧姆是指信号源的阻抗,还是从本级向前一级电路看进去的等效源阻抗?以实现输入阻抗匹配。是不是每一级都要考虑阻抗匹配?这样不就损失了6dB了。

是不是在高频或者射频段才考虑输入端、输出端阻抗匹配,以避免发生反射。在低频段,放大器之间的级联一般是不用考虑级间匹配吗?也就是放大器输入端不用接50欧姆到地,以及输出端不用串联一个50欧姆电阻到下一级。放大器之间直接级联,因为用一般放大器放大,输入阻抗都很大,输出阻抗都很小。也就是下图:

在多级放大电路中,前级只要考虑电压放大就行了,不用考虑级间匹配,在功放电路才考虑阻抗匹配,实现最大功率传输,我这样理解对吗?

求解答,万分感谢!

亲;不对呕。射频放大器即便放大直流信号也是需要匹配的。这主要是放大器带宽问题,与信号关系不大。

那这样的话,输入端会损失6db,输出端也损失6db了。

亲;单级放大,确实如此。多级放大时,级间不一定需要匹配。

放大器的级间连接,为什么不一定需要阻抗匹配?

而且我在想是不是PCB布线的线宽也会有有特征阻抗,即使用特征阻抗是50Ohm的转接头连出去也不一定会有匹配?

最近被这个阻抗匹配的问题搞的有点乱,希望能给出比较全面的回答。

有点啰嗦= =。

阻抗匹配理论;来自波的反射概念,这个概念需要满足一些条件。否者不成立。所以;有些时候,一旦满足一些条件就可以不匹配。