关于运算放大电路中的阻抗匹配

请问下TI的技术人员,在实际的高速(上MHz)电路中,运放之间需要考虑阻抗匹配吗,比如前一级运放的输出和后一级运放的输入之间需要考虑阻抗匹配吗?另外,在实际实验过程中发现对单个运放做简单的放大操作,用同轴电缆连接到示波器上时,示波器需要调节终端电阻为50Ω或75Ω波形才可以正确显示,这是不是就是阻抗匹配?

楼主你好,阻抗匹配在高速或者长距离的情况下都需要考虑。前一级跟后一级运放之间要不要阻抗匹配也不能一概而论。如果两运放之间连线的长度大于十分之一的信号在走线中的波长的话,就得考虑阻抗匹配的问题了。

如果示波器探头设置为了高阻输入(一般情况下是1M以上),那么信号在示波器输入端就会产生反射。为了防止反射就应该端接跟探头线特征阻抗同值的匹配电阻。对于一般的探头,端接50欧即可,此时阻抗匹配。

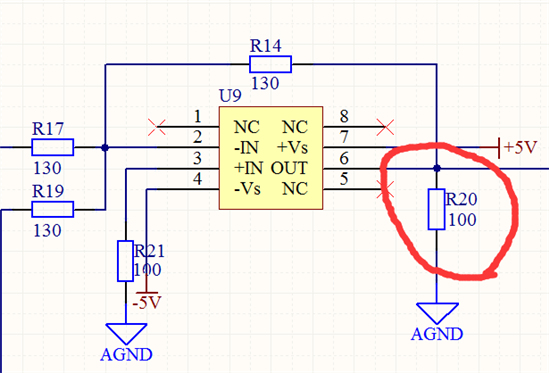

恩,我还发现在有些运放的输出端会通过一个电阻接地,如下图所示,请问为什么要这样?这个电阻的作用是什么?

您好,请问这个电路是在哪里看到的,应用在哪里的?后级电路是什么?

如果只给出这张图,我还真不知道这个电阻有什么作用,除了增加系统的功耗…

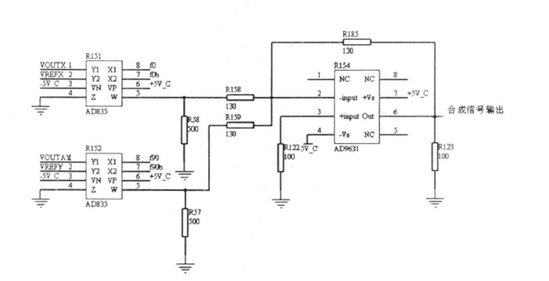

恩,是在一篇论文上看到的,他用的AD的乘法器芯片AD835和AD9631这款运放芯片来合成信号,下面是电路图,但是最后AD9631的输出端接了个100Ω的电阻不知道是干嘛的?您能帮我解答一下吗?而且他的这篇文章中貌似每个运放的输出端都通过一个小电阻接地。

AD835是带宽很宽的模拟乘法器,在这种速度如此高的场合,看来这个地方的100欧姆电阻极有可能就是端接匹配电阻了。可以通过控制PCB走线的宽度,来使得走线的特征阻抗为100欧姆,在负载端接100欧的端接电阻即可防止输出信号的反射。

那像这种高速的运放电路,是不是一定得在输出端接一个匹配电阻,将该电阻接地呢?如果需要,一般这个电阻取多大有没有什么要求?

是否要端接看情况而定,距离很长或者速度很快的情况下就要端接。

电阻的取值要看pcb layout出来之后走线的特征阻抗。

关于如何控制走线的参数,使得走线的特征阻抗等于某一设计的值,请参考TI的文档SLLA284A的layout部分。

一般MHz还好,因为示波器输入探头的寄生电容,会导致宽带运放不稳定。