关于放大小信号的问题

刚开始接触运放一块,有个很基础的问题,网上查阅了很久,一直都是一知半解,望大伙不吝刺激,先谢了。

单电源运放现在用的很火,目前做一个项目,电池供电,所以选了ti的一颗opa333,单电源,低功耗,低电压。

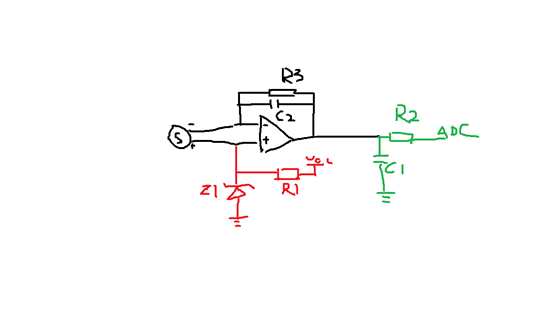

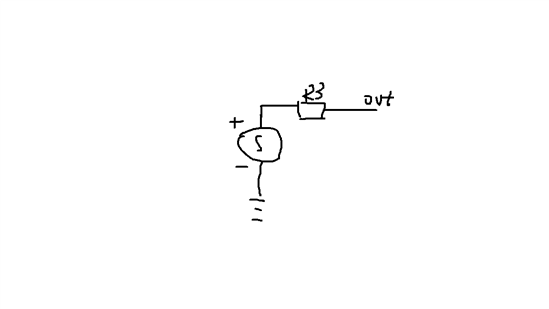

主要目的是放大一个传感器出来的小电流信号,电流是nA级的,电路图见下。

S是传感器,红色部分是提供直流偏置,绿色部分是低通滤波到后一级adc做采样。

偏置问题:

1 红色部分是用一个稳压管做稳压,那作为偏置,最终+极的电压不应该是(Vsenor+Vref)吗?稳压管这么一稳压,不是永远是稳压管的稳压值了,还何来叠加(不超出稳压管能力范围)?当然上图是一个差分运放,减法器,但是我网上浏览了很多,单端放大也很多这样用。

2 看到用电阻分压然后做直流偏置的。1的坏处是偏置电压必须随着稳压管特性,电阻分压是可以随意你想要的值。但是由于运放的偏置电流的存在,会导致电 阻分压点的电压值略偏低于理论值,当然opa333的几十pA的电流我这里可以直接忽略了。问题是这样的设计我接上传感器后正端的波动很大(100K的分压电阻,有50mv左右的波动),运放输出也有波动(40mv左右),并不是我所期望的(期望在1mv以内的波动)。

然后我就直接在分压电阻那个稳压点并联了一个4.7uf电容,整个现象似乎是趋于我的期望了。

问题:2这种做法直接并电联可取吗?电容值取多大有讲究吗?2和1是否区别很大,因为1的正端是基本钳住在稳压管的值,2是叠加?

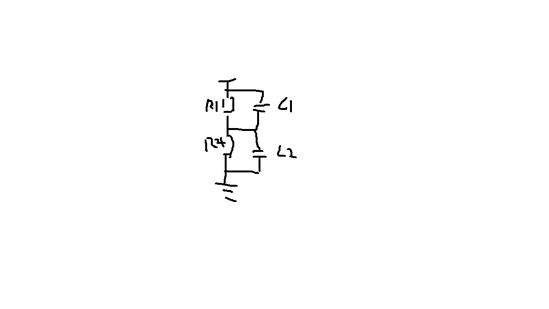

看到分压有一种说法,见下图:

电阻分压做偏置要保证R1*C1 = R2*C2,这种说法的理论依据是什么?

低通滤波问题:

绿色部分仅作为低通滤波吗?看到之前有说运放出来不能直接接Σ-△型的ADC,其他还有和作用?

放大倍数问题:

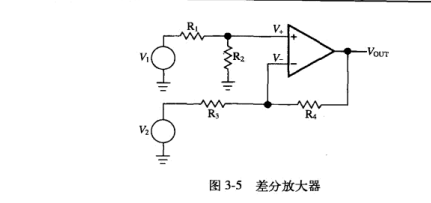

标准差分放大器应该差不多是这样,Vo = (V1-V2)R4/R3

但我画的那图(传感器提供的参考电路),没有类似上图的R3,怎么计算放大倍数?

共模抑制问题:

差分放大器需要共模抑制,我记得在上图中需要R1*R2 = R3*R4。那传感器提供的那图如何做?

不好意思,一下子很多问题,大神帮我分析分析,知道的朋友回答一个两个也好的,万分感谢了~

亲,建议你用电阻分压做基准。稳压管阻抗包括反电势部分内阻部分和漏电流及PN反电势及噪音源。这些都是温度等背景函数。不适合精密放大偏置。由于参考源内阻及噪音影响,需要在参考源并旁路电容。容值一般在103~105之间。

好的,多谢兄弟。

电阻分压做偏置要保证R1*C1 = R2*C2,这种说法的理论依据是什么?

有听过上面这样的理论吗?

这是响应平衡设计。RC并联后交流响应时间常数为RC积。响应一致保证了即便在上电阶段,参考点电压和电源电压比值恒定。

厉害!

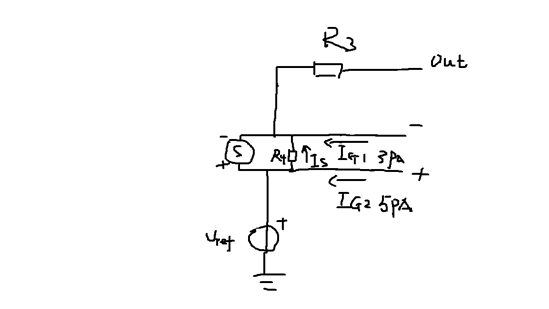

再请教下,第一幅图中没有第三幅图那样的R3电阻,我放大倍数怎么做理论计算?是直接用senor的内阻吗?

亲,这是电流放大设计。将源在短路状况下的电流信号放大成电压信号输出。

运放在线性区工作时,可以看作输入端开路;同时也可看作两输入端短路即虚短。从虚短看,信号源短路输出。短路电流从R3及其并联支路流到输出端。R3反馈网络阻抗与源短路电流积(包括矢量)即为输出电压(矢量)。

xp,您好!

非常感谢,茅塞顿开。

是否是这样理解,上图手绘的等效电路为:

R4是0欧姆(虚短),Is流过R3产生电压,在Vref上做叠加。

1 如果这样看,那在这条通路上电势是越来越高的,R4被等效成了0欧姆,实际应该等效个几欧姆吧,那么+端的电势不是低于-端了吗?运放不是工作不正常了?

该如何理解或者怎么等效?

2 根据实际情况1肯定不是那么理解的,实际+端肯定是高于-端,运放才能正常放大。我现在的目的是尽量拉开Vref到Vcc的压差,提供更大的采样空间,那既然Vref可以动,我是否能将其直接接地?等效电路就变为如下:

似乎看着也挺合理,但是考虑到正端接地了,依据正端电势大于负端才能工作,那么负端电势变为负了,本身整个电压为0-vcc,似乎不合理。

这个该怎么理解?