高速运放4层PCB叠结构请教

时间:10-02

整理:3721RD

点击:

大家好,我想问一下,对与高速运放,以下两种层叠结构,各有什么优势?

层叠1:SIGNAL GND POWER GND 注:POWER包含正负电源,共用一个叠层;

层叠2:SIGNAL VEE VCC GND 注:正、负电源各占用一个叠层。

亲;多层板是把双刃剑。它带来便利同时也容易造成过渡耦合及噪音等问题。电源层并不是一铺而就,否则问题更多。

你好,关于过渡耦合和噪声问题,能具体一点吗?关于布局和电源层的走线、噪声控制,请指教!

亲;信号线是导体,电源层也是导体,两者夹着绝缘层,这就是标准的电容。频率低时,因容量小;阻抗很高而忽略,可高频下的阻抗就不再高了。

亲;大面积电源层因面积增加而使容值高于传统,多层结构减薄了介质厚度。。。加之肌肤效应,处理不好,简直雪上加霜。

亲;这就是“不能一铺而就”的原因。高频PCBlayout是门艺术也是电路的再设计,需要谨慎。

这两种层叠结构谁的好的,连个都是高速信号!

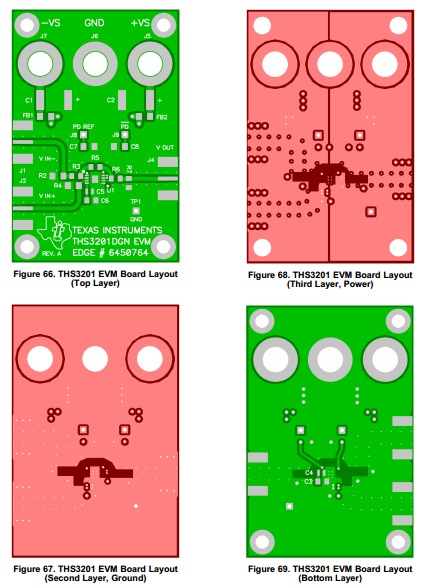

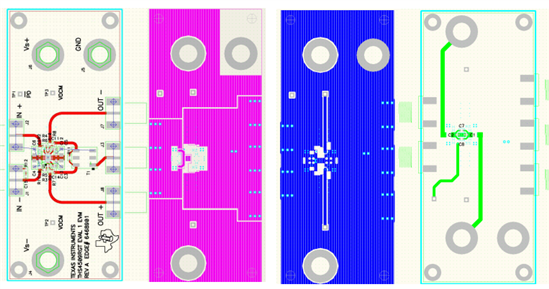

其实,TI的评估板上把高速信号地层和电源层都挖空的原因是减少分布电容。在高速电路上,分布参数的影响非常严重。你可以在你做好的板子上,人为的加入一个1pF, 2pF的电容做分布电容,然后测一下其频响特性。相信,对分布参数的影响会非常非常深。