+放大器中的容性负载

时间:10-02

整理:3721RD

点击:

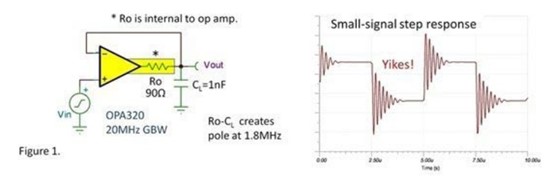

麻烦制造者”运算放大器开环输出电阻 (Ro),实际并非运算放大器内部的一个电阻器。它是一个依赖于运算放大器内部电路的等效电阻。如果不改变运算放大器,也就不可能改变这种电阻。CL为负载电容。如果想驱动某CL就会受困于Ro 和 CL 形成的极点频率。G=1 时 20MHz 运算放大器的反馈环路内部 1.8MHz 极点频率便会带来问题。请查看图 1。

图1

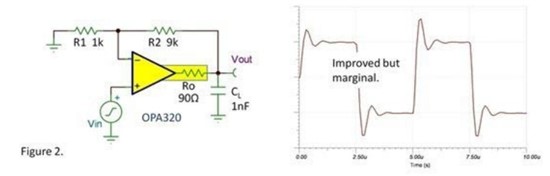

对于这个问题,有一种常见解决方案—调慢放大器响应速度。想想看,环路具有固定的延迟,其来自 Ro 和 CL。为了适应这种延迟,放大器必须更慢地响应,这样它才不至于超过去,错过希望获得的终值。减速的一种好办法是,将运算放大器放置在更高的增益中。高增益降低了闭环放大器的带宽。

图2

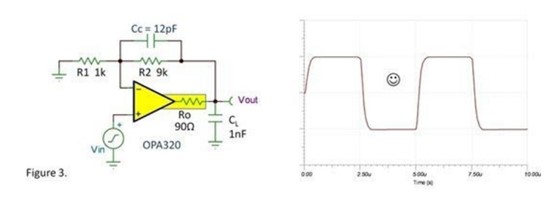

图 2 显示了驱动相同 1nF 负载但增益为 10 的 OPA320,其小步进值的响应性能得到极大提高,但仍然很小。将增益增加到 25 甚至更大,似乎相当好。但是另一个问题出现了。图 3 增益仍为 10,但增加了 Cc,其将速度又降低了 1 位。Cc 过小时,响应看起来更像图 2。Cc 过大时,可能出现问题,其看起来更像图 1。

图3

这里简要讲述了运放的输出复杂为电容时, 输出电阻电容的极点而引起的问题. 需要设计时注意