+带条纹的电容

时间:10-02

整理:3721RD

点击:

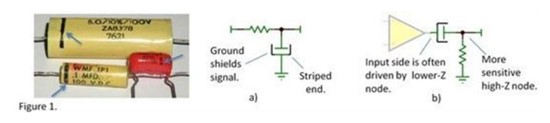

薄膜电容外层的导体屏蔽了内层的导体。在一个简单的低通R-C电路中,如图1a所示,电容带条纹的一侧接地,从而屏蔽了电磁耦合和电磁干扰。对于高通R-C电路,如图1b所示,电容两端都没接地。但总体上看,前端驱动呈低阻抗特性,这将不容易受到感应噪声的影响。因此,应该将带有条纹的一端连接至低阻抗侧。

图1

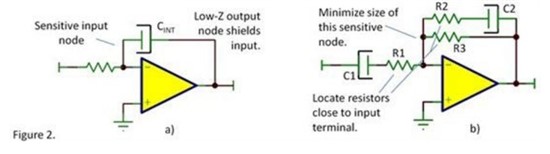

现在来看看积分电路。如图2a所示,积分电路的积分电容由低阻抗的运放驱动,这种连接不容易受到外部干扰的影响。在这个电路中,反向输入端显然是敏感节点,因此带条纹的一端应该连接到运放的输出侧。

图2b所示电路的布局需要考虑更多的内容。C1 和 R1的连接顺序不同则结果也不同。R2和C2也是这样。理论上,不同顺序的连接不会有什么不同,在SPICE仿真的结果也一样,但小体积的R1 和 R2可以靠近反向输入引脚放置。这样可以减少产生天线效应的区域和敏感区的寄生电容(这个寄生电容会影响到系统稳定)。大体积的薄膜电容C2跨接在运放输出端和反向输入端之间,带条纹的一端接在运放输出端。

图2

首先,布局需要考虑的是那些对干扰敏感的模拟电路,其中有些干扰源是潜在的。其次,精心的布局和调整器件的端口可能会提高电路的性能。这里调整器件的端口并不仅仅是对调电容带条纹端口和不带条纹端口的问题。在系统中还可能有其它大体积的器件会吸收噪声和辐射噪声。当意识到这点后,就能有指导性的调整并改进PCB布局。

带条纹的电容是个提示,它提示我们还有许多关于电路板接地、信号回路、器件选型和布局的知识需要去了解。许多数据手册上提供了帮助我们优化性能的具体措施。

不曾关注过的细节. 谢谢

很好的器件资料.