传统运放外部电阻补偿偏置电流的一点疑问

时间:10-02

整理:3721RD

点击:

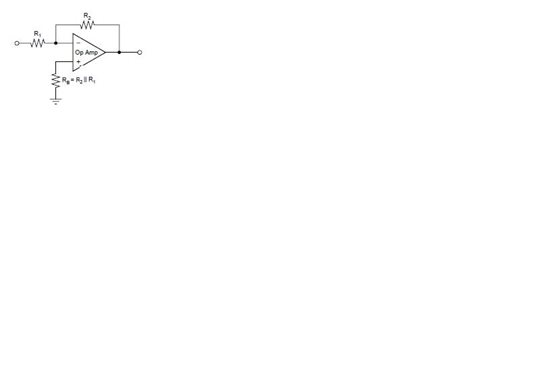

一般传统的运放会利用外部电阻匹配来减少偏置电流的影响,如图所示。我现在的疑问是运放正负输入级的漏电流是不相等的,那为什么还要用匹配的电阻呢,这

样能够达到减少电流的影响么。 刚开始学习运放的知识,希望大家给予帮助,谢谢。

你好,平衡电阻的作用是使两个输入端的对地电阻保持一致,这样可以尽量避免运放的偏置电流引起的附加的失调电压

这种做法有一定道理,但是也不能适用于所有的电路。

要根据偏置电流引起的误差,与,运放其他指标(如Vos)相比,是否有较大影响。

因为,如果Ib引起的offset相比于运放本身的Vos,要小的多的话,那么这样做意义不大。而且会引入一下不确定的噪声或者误差。

如果偏置电流引起的误差,与,运放本身的Vos指标,相当或者更大,那么这样做是有一定效果的。

当前,运放工艺不断提高,主流运放的Ib也都比较小了,如COMS、JFET型的,有的可以达到fA级。

你好,请问IB引起的offset怎么计算呢,是直接用IB乘以运放引脚连接的对地电阻值么

你好,这样的乘积是在输入端引起的偏移电压,要换算到输出还要乘以放大倍数。另外对于初学来讲碰到的一般都是双极结型的常用运放,这个匹配电阻还是有这个必要的,当然以后你接触多了会知道CMOS输入型的以及一些偏置电流与失调电流差不多大的高精密运放是不需要这个匹配电阻的

对于结型来说,运放两个脚的ib+与ib-不是不同么,在计算由于IB引起的失调时,与ib+与ib-的关系是什么呢

两者之差是计算失调的依据,要是相同那就不会引起失调电压了哦