信号叠加的解决办法

您好,

我使用FPGA产生一个5MHz的时钟信号,0V-3.3V。为了测试产品的稳定性,需要在这个时钟信号的低电平位置叠加一个脉冲信号,此脉冲信号也是由FPGA产生,频率约为250Mhz。

我的问题是:

①:怎样控制脉冲信号的幅值,使其可以在0V到5V内可控?如需选用放大器,请问我需要的放大器的带宽满足什么条件?

②:怎样把脉冲信号叠加到时钟信号上?

③:怎样把反向脉冲信号(一直是3.3V,当有触发的时候为0V,250MHz)叠加到5V的直流电源上?

④:我把5M的时钟信号分别经过TLE2072(做跟随器)和THS3062(跟随器)这两个运放组成的跟随器,但是输出的时钟信号完全变形,类似于三角波。请问这是为什么?

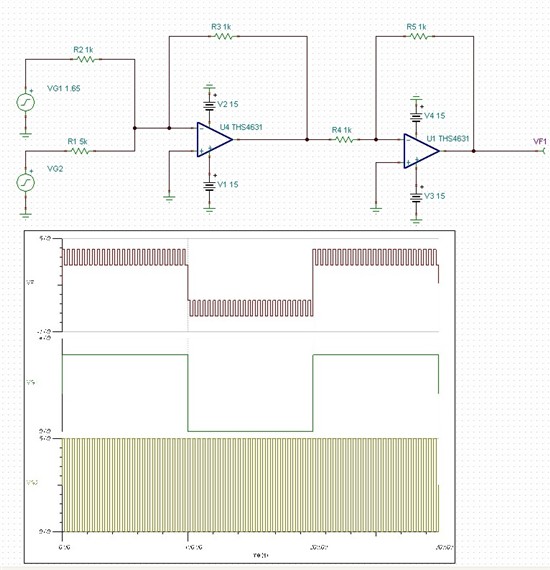

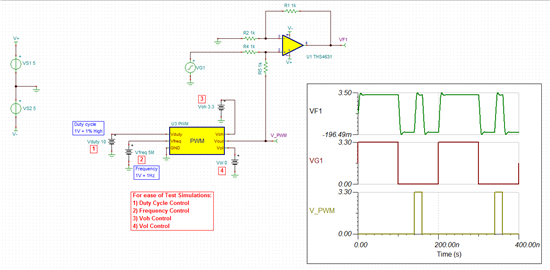

您需要选择的运放需要有高电压,高带宽的放大器。下图是利用THS4631为您搭建的加法器,VG2是加入的250Mhz脉冲,如初始值是5V的话,通过增加R1可以减小VG1,gain=R3/R1。 具体使用细节如反馈电阻大小等再参照data sheet。

其它也有更多的选择,您可以直接在我们的官网上的高带宽运放中选取。

您的第4个问题应该是受到TLE2072带宽的限制造成的。

首先,谢谢您的回复。

关于第四个问题,我觉得是带宽的问题不太大吧,因为我还把5MHz的信号通过THS3062,跟随器的效果也是很差很差的呀。

同时THS4631的带宽也不太够呀。我产生的250Mhz是矩形波信号,如果我用电阻调节这个矩形波信号的幅值后,带宽就稍显紧张了。

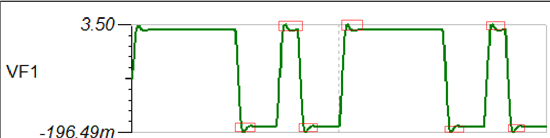

最后,请问您是用TINA-TI模拟的吗?下面是我模拟出来的信号图。完全不对啊。目标使3.3V直流电与250Mhz矩形波信号叠加。

您好,谢谢您的指正。

从波形来看我在仿真的时候的确没有设置好参数。所以按照您的结论THS4631 满足不了要求。

您是否可以告诉我具体FPGA输出的是哪两种信号? 一种是0~3.3V的时钟方波信号,另一种脉冲信号波动范围是多少?按照我给您 的线路仅是在0~5V 脉冲输入的前提下,这个时候调节增益就可以满足您前面提到的 0 到 5V( 达不到0V ) 幅值变动。 如果脉冲信号 不是0~5V,那么想要实现0到 5V 的幅值就复杂的多。这里的线路仅是加法器而已。运放必须在power supply 和 带宽上同时满足要求而且需要非常高的SR,脉冲周期如果是4ns,每一个脉冲只有2ns。目前我还没有看到合适的。 测试稳定性一定要叠加的脉冲没有失真吗?

第4个问题对TLE2072应该是带宽问题,对于THS3062,您是否有注意其是电流反馈放大器,做跟随器的时候线路是如何连接的?是 否有在反馈路径上串联一定电阻? 这个问题请具体看一下datasheet中关于Unity Gain的介绍。

您好,我使用的FPGA产生两种信号,一种是0-3.3V的5MHz时钟方波信号,另一种是250MHz的,幅值变化0-3.3V的脉冲信号。

测试需要仅仅需要使时钟信号上叠加的脉冲信号满足上升时间和下降时间以及脉宽没有很大变化即可。

另外,在使用THS3062时,反馈回路串联电阻了,严格按照datasheet中的接线的,连接成跟随器。然而,我在正相输入端输入5MHz时钟方波信号,在不接电源时,输出的信号跟我输入的信号差别不大。但是当接上电源时,波形已经完全变形了。

我的供电电源选择了两种:一种是0V,5V,另外一种是-12V,+12V。效果都是一样。

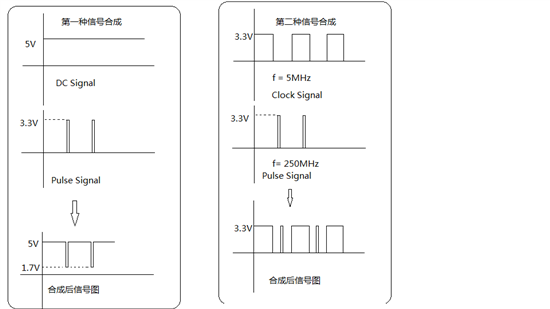

附图说明我想要达到的效果:

第一种信号合成:给直流电平叠加脉冲信号

第二种信号合成:给时钟信号叠加脉冲信号

其中在第一种合成方案时,需要对脉冲信号的幅值进行调节。最主要的是怎样叠加信号?

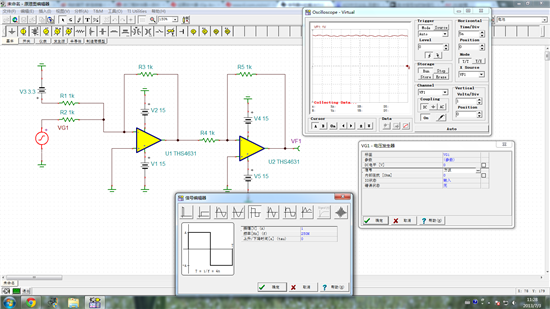

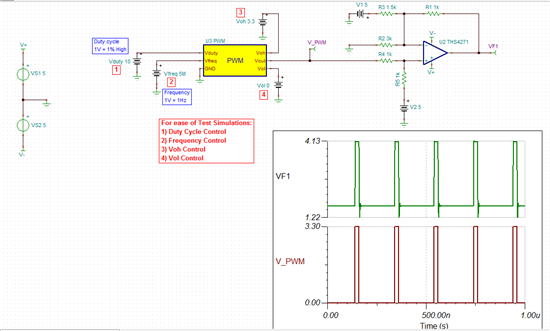

提供一个仿真电路,供您参考:

2022.THS4271_Signal Combine_01.TSC

1263.THS4271_Signal Combine_02.TSC

这个PWM波形发生器,可以模拟250MHz的PWM波形,后面电路的基本功能也是对的,可能还需要改变调整带宽。

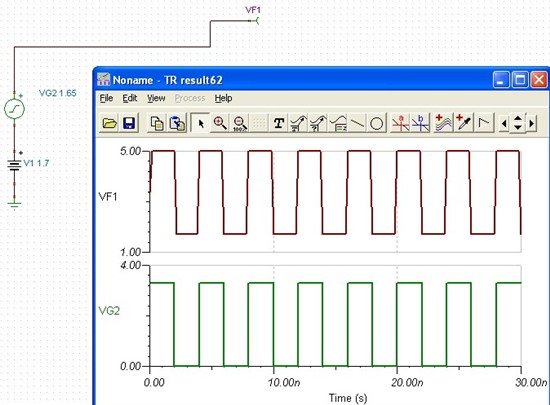

2860.THS3062.TSC

附件是THS3062 的TINA 仿真。在5MHZ 信号输入下没问题,请double check。

看您提供的信号合成说明,您需要的应该不是加法器,运放搭建的加法器效果和之前给您的图基本相似。

而您这里需要的前者像是与非门,后者应该是或门。

首先十分感谢工程师们的回复。

是IC的问题,我重新买了THS3062,就OK了。

我也考虑过使用与非门,然而这类数字器件,只会有H和L之分,也就是当L时是0V,如果有某一种器件可以调节L和H的电平就最合适不过了。

例如有一种IC,2.0V一下的都认为是L,那么我可以在这个IC上叠加一个小于2.0V的REF电平,这样就能达到的想要的结果。请问您是否知道有这样的器件?

谢谢

您好,

第二种方案示意图中脉冲信号的频率和上面的 5 Mhz 并不匹配,其实在clock 信号的high / low 过程中一直伴随着脉冲,在clock 为high 的时候要求输出也稳定为high,当clock 为low 的时候,输出和脉冲信号同步。 所以这个不好用加法器来实现,属于或门功能。

第一种方案,图中DC电压是5V对吧?。这个方案一您前面没有提到过,这个就要看您的设计灵活性和目的是什么,比如下面的例子,这个250MHZ的0~3.3V 信号,我可以加入1.7V 的DC电平,将其输出达到您要的要求,同理如果改变信号到0~2V,可以额外加入3VDC。 其实简单来说可以是将脉冲信号反向后再抬高5VDC。实现方法有很多,如用运放搭建的加法器,只是如果脉冲信号带宽是250Mhz,器件的带宽和slew rate 较难满足。您说的那种逻辑芯片指的是什么样的?如有必要麻烦您再解释下。

谢谢。

经过放大器拉长了我的上升时间,这个是不能接受的。我去买芯片实际测试吧。

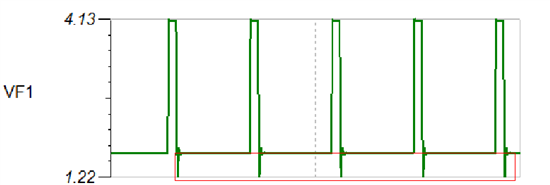

还有一个疑问,我经过施密特触发器能否将图中的红色框中的超调等等滤除呢?

楼主您好,尖峰一般都是可以尽量消除的。

Iven 为您提供了很好的加法方案。

但请注意用的是5MHZ 的脉冲,如果是250Mhz 的脉冲,请看一下上一个回复您的内容。

哦,抱歉,我前面没解释清楚。第二种方案直接用FPGA比较好实现。

第一种方案,可以将脉冲信号反向后加入一个DC电平,我的问题就是怎样把这个250MHz的脉冲信号加入到DC电平上?没有找到合适的OP放大器。第一个要求是需要叠加以后的信号上升时间,下降时间,占空比尽可能不发生变化。我的第二个要求是:控制脉冲信号的幅值,也尽可能的不改变脉冲信号的幅值。

对于第二个要求,我的想法是,通过FPGA输出,然后经过某一种逻辑IC,这种逻辑IC带VREF参考电压。比如正常的逻辑IC在High/Low分别对应5V/0V,加入VREF = 2.0V后,High/Low分别对应5V/2.0V,或者加入VREF = -2.0V后,High/Low分别对应3V/0V。想法有点奇特。

语言表达能力欠缺,请见谅,谢谢。

您好, 应该有更好的办法但我不熟悉。

您提到的逻辑器件没见到过,而且一般输入和输出是同时参考电源的。

对于第一个方案,您的FPGA内部是否可以直接做反向?如果不可以那就需要外部芯片来做反向,至于加入DC电平,如果是外部恒压源的话可以直接串联。就像前面提供给您的那种简易的方法。