求扫盲,上拉电阻的问题

今天调试电路,来了一个高手(至少比我强吧)。测量输入的电压不够,说需要上拉电阻。我突然对上拉电阻的理解模糊了起来,请专家帮我从电流或者本质一点的角度帮我理解一下。什么时候需要强上拉,弱上拉,上拉是怎样具体实现的(IO口内部是怎样感受上拉的?电流在IO口内部的电阻上将电压拉高了么?),在数字电路中的一些常用情况?谢谢专家

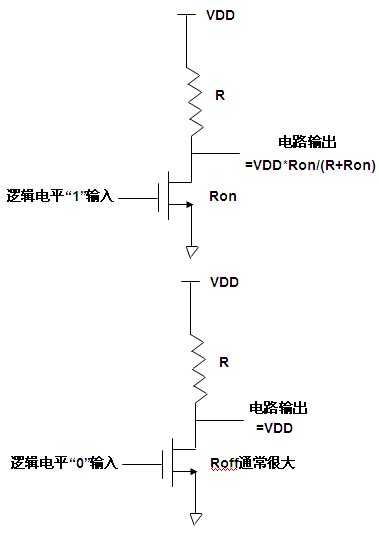

如下图,上拉电阻是R,晶体管导通电阻Ron,电路的输出是VDD*Ron/(R+Ron),以及VDD。通常Ron比较小,所以输入为1时,输出近似为0。

您好,

add, 您可以将这种能力看做电流,外部增加了一个上拉,就等于增加了一条电流源,对于输入或者输出这条主干来说增加了额外的电流,当然驱动能力就会相应的增强。增加的电流强弱当然受上拉电阻阻值的影响。同理下拉也是这个道理。

上拉电阻的应用是要看I/O内部结构而定的,并不是想怎样就怎样,太强和太弱都是不合理的。

另外有的上拉也可以用来调节信号的sequence,让信号拥有更快的上升沿,而且还可以用其它电平做信号的“驱动”。

谢谢,这些我倒是都想的到。“上拉电阻的应用是要看I/O内部结构而定的”,我其实是想问这句。

个人觉得分两类即可,一种就是内部有pull up/low的,这种结构严格来说外部是不需要上拉或者下拉的,需要外部再次pull up/low目的就是增强驱动。很多IC 在设计的时候考虑到功耗等因素,在内部是weak pull high,同理为了外部不会消耗太大能量而weak pull low,这个时候就会需要外部的double pull up/low 来使系统稳定,更多的是让设计者觉得安心。如果外部和内部是相反动作就会变成分压。所谓调节sequence,其实就是利用到drive能力越强,rise/fall time就越快。

另一种open drain结构,这种结构在内部没有任何pull high/low,一般就是两个管子互补接在一起做输入输出,如一般的GPIO引脚,这在使用的时候外部都会给一个有效电平作为初始状态,强度大小主要受供给其它连接的芯片来决定。

简单就描述这些,不知道是不是您想要知道的,具体应该会有专门的归纳资料,您可以网上搜看看。

讲的很好,谢谢您