关于PT的一个小问题

我尝试这样做了,然后link_design命令之后则在log文件中出现

Warning: Unable to resolve reference to '####' in '*****'

####为子模块,****为顶层模块

不行,read_verilog 会指定或判断是rtl code还是netlist,你这么直接cat起来在DC按rtl算,在PT会认不出的,标准的做法是吧底下的模块网表转成db或lib,直接做link_libray就可以了

那顶层模块只是例化了这些子模块,顶层模块是rtl,这些子模块是网表文件,这样对其进行cat也不行吗?PT不能识别吗?

那你说的把子模块都转化成db或者lib,那我的顶层模块还是rtl,这样pt就能识别了?

回答的人怎么不回复啊?

你把rtl跟netlist 直接文本操作到一起当然不行了, pt严格确认读进来的文件格式的,转成lib后,只是个timing model了,不再有rtl和netlist的概念了,当然可以了

那顶层模块就直接是rtl了,不用管了?

那最终输入PT的文件就是这样的

top.v(rtl文件,verilog代码,里面例化所有的子模块)

所有的子模块分别以自己模块名来命名的lib文件,DC转成db

link 所有的子模块的db文件

如果不是,可以稍微详细地说明一下吗?我比较笨,不是很明白你说的

小编为何不把top和sub module用DC一起综合了再用PT检查Timing?还这么麻烦,DC综合一部分,留一部分的?

哪怕用DC工具先read,再write出来也好啊

怎么将网表文件变成lib文件呢,我没见过啊

关注下

学习了~

请问一下 我用的是门级网表的.v文件 为什么也出现了和小编同样的问题呢 看您能不能看一下

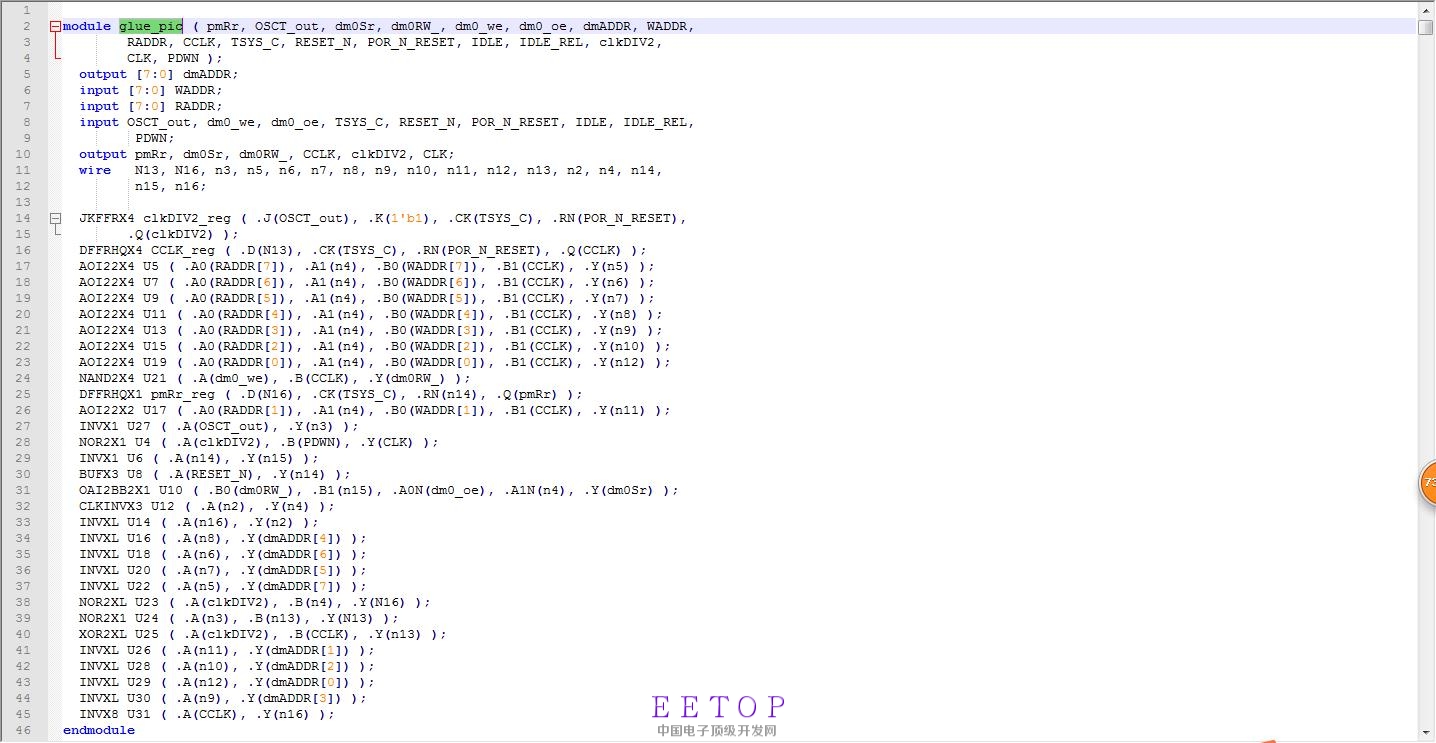

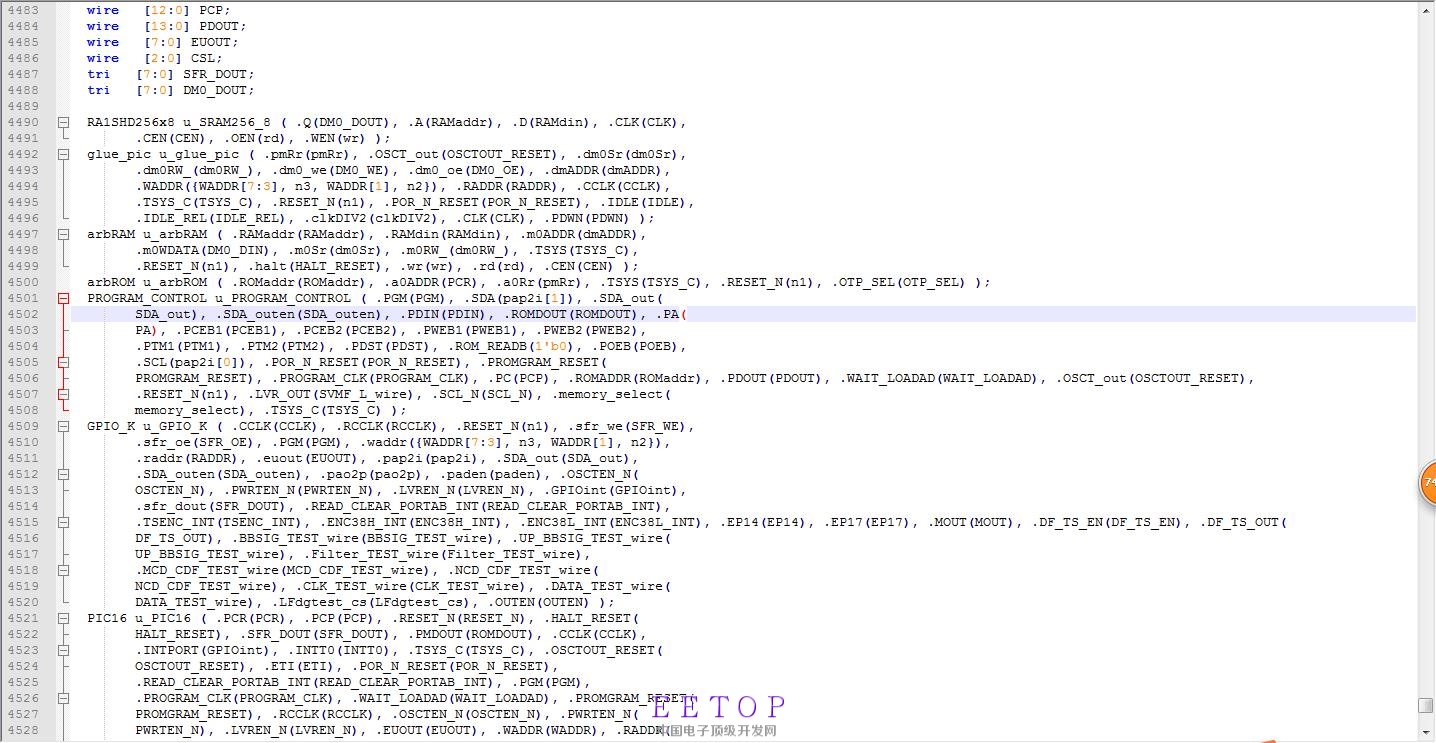

read_verilog MCU52.v

其中MCU52.v这个文件是DC综合后write出的一个门级网表文件,在该文件内顶层模块叫MCU_TOP,顶层模块之下有很多子模块,

比如glue_pic,arbRAM等,但现在就是说这些子模块 Unable to resolve reference

!我的问题和你的一毛一样!麻烦问一下现在解决了吗?

紫薯布丁