verilog里的time step是怎样的概念?

但是没找到关于time step的明确定义。

新手请教如何才算一个time step呢?

“非阻塞赋值使用一个小于等于号“<=”。“非阻塞赋值”由它的赋值操作行为而得名:在一个时间步(time step)的开始估计RHS expression的值并在这个时间步(time step)结束时用等式右边的值更新取代LHS。在估算RHS expression和更新LHS expression的中间时间”

谢谢。我之前看书看错了,导致理解错误了。

顺便再问一下,如果有连续两个阻塞性赋值语句,它们的时间间隔是不是最小时间精度?

你所说的时间精度是指 `timescale 1ns/10ps类似这样的吗?

阻塞赋值一般在RTL中指的是组合逻辑,这个我们认为是不需要时间的。

在testbench中,我们也认为是立即赋值的。

你加我q吧,大家讨论一下,感觉你的理解有点跑偏了。

新手,不好意思占你很多时间。

和阻塞性非阻塞性赋值没关系,我是想问,顺序语句块里的两个不相关的语句,它们的执行时间和先后顺序有关系吗?

按说顺序执行应该是有一定的时间间隔吧?还是完全取决于前一句完成的时间?

它们有没有可能同时执行?

PS:1、后面这些问题和标题已经木关系了。

2、非常感谢你的耐心解答!

1、对,不相关的木关系

“它们的执行时间和先后顺序有关系吗”没有关系。也没有你说的时间间隔。新手怎么就在扣赋值时间间隔呢,快哭了都。

“按说。”其实,在C语言里这是有关系的,verilog只是语法跟它很像,但是verilog要综合成电路的,还是有差别的。

“ 它们有没有可能。”很有可能哦,亲。

组合逻辑:直接赋值,大家谁也不等谁。

时序逻辑:DFF在时钟沿到来的时候采样。

2、我也从新手过来,虽然现在还是新手。

自我感觉这个东西需要身边有人给你指点,自己刚开始学很从一个语言转到电路的过程比较痛苦与郁闷。

3、如有误,请尽情拍砖。

明白了!

太弱的问题不好意思问认识的人。 还好有网络

囧~。

谢谢解释,我也需要

thanks so much

你好啊。我也同意你对于time step的解释。但是我有一个问题想麻烦你帮我解答一下。

非阻塞赋值正是因为在time tep结束时才更新LHS,所以才导致我们用非阻塞赋值语句对变量赋值时会有延迟一个周期的现象。

但是为什么我们在写rst下降沿对信号进行复位时,不会产生延迟?

应该不是指一个时钟周期。感觉time step就是在RHS的变量更新之前赋值给LHS的时间。“非阻塞赋值正是因为在time tep结束时才更新LHS,所以才导致我们用非阻塞赋值语句对变量赋值时会有延迟一个周期的现象” 没有延迟一个周期的现象,可以仿真试一下。RHS付给LHS的值是其上一个时钟沿采样的值,跟这个不要混淆。

“但是为什么我们在写rst下降沿对信号进行复位时,不会产生延迟?”等效于电路中寄存器复位

简单的测试程序貌似真的米有延迟。但是麻烦看一下以下两段代码

1.

//摘自我最新在写的一个程序

always @(posedge clk or negedge rst)

begin

if (!rst)

hint <= 1'b0;

else if ((current_state == 1'b1) &&

(bitstream == 2‘d60))

hint <= 1'b1;

else

hint <= hint;

end

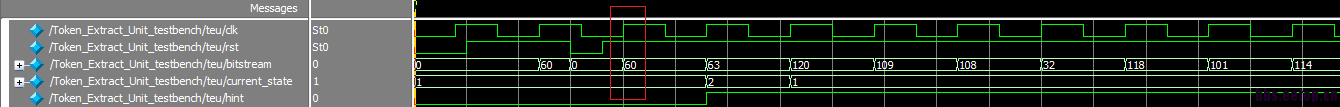

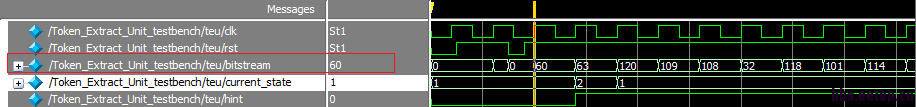

波形图如下图1

可以看到红色矩形处的clk上升沿,已经满足了else if的条件,但是hint延迟了一个周期跳变为1

于是我写了以下简单的测试代码

2.

always @(posedge clk or negedge rst)

begin

if (!rst)

a <= 1'b0;

else

a <= 1'b1;

end

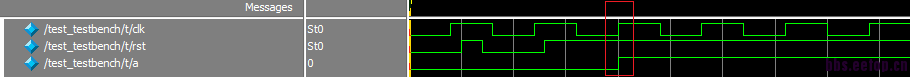

波形图如下图2

可以看到红色矩形clk的上升沿处,a的跳变没有延迟。

可以解释一下这是为什么吗?我百思不得其解。

谢谢了~

if ((current_state == 1'b1) &&

(bitstream == 2‘d60)) 在你标出的位置clk采样时bitstream == 0,到下一个周期才满足else if 条件。不对吧 你看左边的值 bitstream是60啊

。你说的有道理,但是遇到这种情况,那个值不能说明软件在这个时候采样就是60。一般来说它是采时钟沿前的值的。

嗯 貌似也只能这么理解了

就是因为这个现象,所以我会对下面的语句

always @(posedge clk or negedge rst)

if (!rst)

a <= 1'b0;

… …

a能及时复位感到奇怪,if(!rst)不会采到rst下降沿前的值么... 呵呵呵呵,不会的。这么设计就理解成dff的reset就好了。如果非要说按照仿真的角度理解这样的问题我也是根据仿真经验,也没见到什么文档介绍过。估计这样的问题会在ieee的standard里有描述,自己感兴趣就多查查看看。查到了告诉我一声

The step time unit is equal to the global time precision. Unlike other time units, which represent physical

units, a step cannot be used to set or modify either the precision or the time unit.