外部RC振荡器的电阻电容问题

时间:10-02

整理:3721RD

点击:

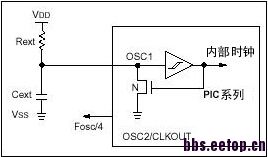

上图是一个外部RC振荡电路,外挂不同的电阻电容会得到不同的频率,如果加大电容的容值,则相同的电阻情况下,给电容的充电时间会变长,这样频率也会变慢,是不是这样出来的波形更好看一点?

我现在验证下来,加大电容的容值,干扰会更大,还会出现死机的现象。

各位大神们,求解啊,是不是电阻电容要有一个合适的配比啊,比如,电容选择在什么范围,电阻选择在什么范围,为什么啊啊啊啊!

那种干扰怎么在外部避免啊,除了电源地之间加电容滤波。

为什么没有人啊,哭出来了

加大电容的容值后,电容点的电压变化率减少,电压在比较器阈值的停留时间越长,因此受到的干扰当然越大。

如果要减少频率,可以在电容与OSC1间加串阻,增加电容放电时的时间常数。

加串阻是直接加在模拟设计电路里,还是在外围电路上加啊,加上串阻,电流不会更小吗?这样充电时间不是会更长吗?小白求指教!

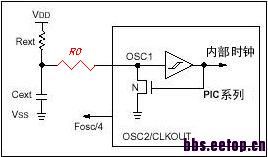

可以加在外围电路上。

电容充电时N断开,R0断路,时间常数由Rext与Cext决定。

当电容放电时N打开,时间常数由R0与RN与Cext决定。

一般来说RN是比较小的,R0加RN比Rext要小些。