有图有真相,求指点!

时间:10-02

整理:3721RD

点击:

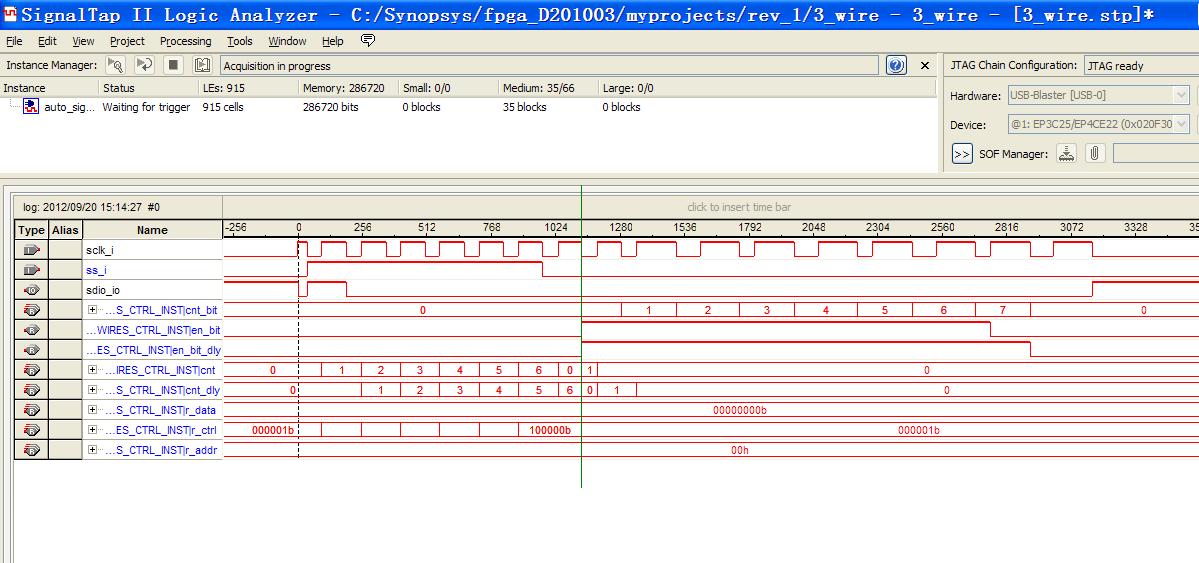

最近在用FPGA对设计的代码进行验证,却遇到了让我捉摸不透的问题,先上测试时用SignalTap抓取到的实时数据,然后就此进行问题描述

首先说cnt和cnt_dly,它们的代码描述为always@(posedge sclk_i or negedge rst_n_i)

begin

if(!rst_n_i)

begin

cnt <= 4'b0;

cnt_dly <= 4'b0;

end

else

begin

cnt <= ss_i?(cnt[3] && cnt[2] && cnt[0])?cnt : cnt+1'b1 : 4'b0;

cnt_dly <= (cnt==4'd13)?4'b0 : cnt;

end

end

分析抓取的数据来看,第一个问题:绿线所指的位置,sclk_i的下降沿,cnt和cnt_dly的值为什么会发生变化,并且,此处ss_i已经为0,cnt往后的值应该一直为0才对,问什么会变为1?

第二个问题,说一下en_bit和en_bit_dly,

always@(posedge sclk_i or negedge rst_n_i)

begin

if(!rst_n_i)

en_bit <= 1'b0;

else

en_bit <= (cnt_dly==4'd6)?r_ctrl[5]?1'b1 : 1'b0 : (&cnt_bit?1'b0 : en_bit);

end

always@(negedge sclk_i or negedge rst_n_i)

begin

if(!rst_n_i)

en_bit_dly <= 1'b0;

else

en_bit_dly <= en_bit;

end

en_bit应该是在sclk_i的上升沿,并满足cnt_dly==4'd6和r_ctrl[5]==1的条件下变为1,为什么会在sclk_i的下降沿发生变化,本来en_bit_dly应该比en_bit滞后半个时钟周期,现在却同时发生了变化,并且后仿时都是正常的,这让我百思不得其解,是在找不到问题的原因在哪儿,求高手指点!

没有高人给予指点啊,我自己顶一下吧!

代码看着有点晕 那么多?: