异步FIFO进行数据时钟域切换时,时序错误,请大神帮忙看下

时间:10-02

整理:3721RD

点击:

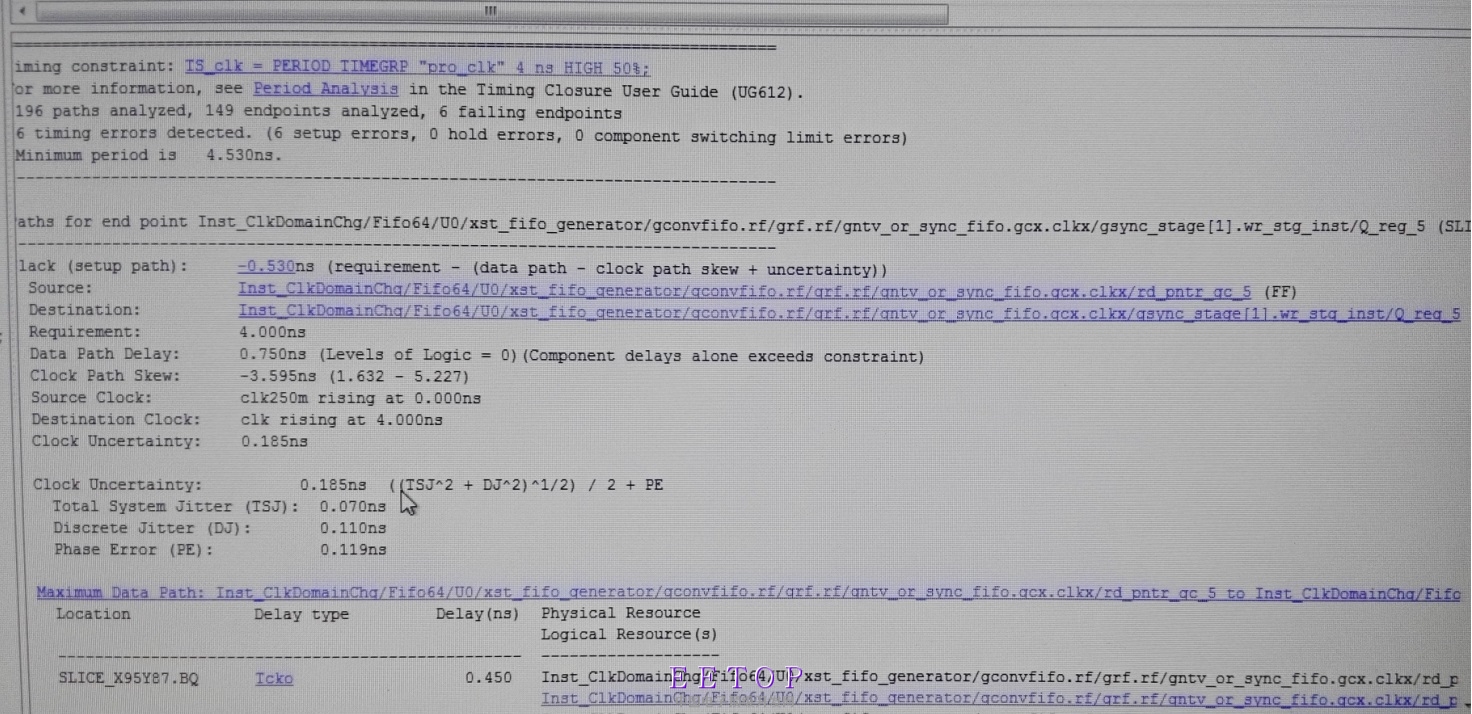

如图所示,FIFO写入时钟是clk,读出时钟是clk250m,都是250MHz速率,clk250m是clk经过pll输出的时钟,两个时钟相位一致,时序报告里的skew很大,到了-3.6ns了,这个肯定是影响时序不通过的主要原因,请教大家,有什么解决的方法吗

求助,只有两个时钟的周期约束,其他约束没有,是不是要添加其他的

3.6ns的skew挺正常的。

你时钟经过bufg了吗,看不太明白时序不满足的具体细节

加入了bufg的,pll的feedback反馈时钟也加入了bufg的,3.6ns的skew感觉真的好大。另外,之前时序分析skew都是对同一时钟进行的,对于不同时钟,不知道是咋算的。之前另一个项目也是同样的用法,但没有报错过

不满足的原因,也是因为skew太大,建立时间不满足要求了

clk250m是clk经过pll输出的时钟,两个时钟相位一致,

-------经过PLL后,clk250m和clk已经没关系了,相位不会一致,不再是一个时钟域,当两个时钟处理吧

1.反馈时钟就没必要再经过bufg了,这不是浪费资源吗。

2.这两个时钟确实是同源的,相位有关系,vivado内部也可以进行分析,这没有问题。

3.但是fifo本身有隔离时钟域的作用,如果时序报错的路径不是必须的,那就tig掉就好了。

具体参见下面的link:

https://forums.xilinx.com/t5/BRA ... IFO-ISE/td-p/810814

好的,谢谢啦,不过feedback加bufg是为了保证pll输入输出相位关系更加严格一些