转眼国庆了,问题还没有解决,狠下心来贴原码求助!

时间:10-02

整理:3721RD

点击:

我用的是Quartus II 5.0,timing仿真过了,但是function仿真过不了!

`timescale 10ns/1ns

module capcard (we,

nrd,

addressbus,

reset,

CS_V1,

CAPING,

CAPSTR,

ICLK,

IDQ,

IGPV,

IGPH

);

input CS_V1,CAPSTR,ICLK,IDQ,IGPH,IGPV,nrd,reset;

output CAPING,we;

output [17:0] addressbus;

wire IGPV,nrd,CS_V1;

reg we;

reg [17:0] addressbus;

regCAPING;

reg [2:0] state;

parameter idle=3'b000,startcapflag=3'b001,//FSM

wait_vstart =3'b010,wait_vend =3'b011,

wait_hstart =3'b100,wait_hend=3'b101,

startcaping=3'b110,read_flag=3'b111;

initial

begin

addressbus<=18'b00_0000_0000_0000_0000;

we<=1;

CAPING<=1;

state<=idle;

end

always @ (posedge ICLK or negedge reset)

begin

if(!reset)begin

we<=1;

CAPING<=1;

state<=idle;

end

else

case(state)

idle:

if(!CAPSTR)

state<=startcapflag;

else if(!nrd)

state<=read_flag;

read_flag:begin

addressbus<=addressbus+1;

CAPING<=1;

end

startcapflag:

if(!IGPV)begin

state<=wait_vstart;

end

wait_vstart:

if(IGPV)begin

state<=wait_vend;

end

wait_vend:

if(!IGPH)begin

state<=wait_hstart;

end

wait_hstart:

if(IGPH)begin

state<=wait_hend;

end

wait_hend:

if(IDQ)begin

state<=startcaping;

end

startcaping:begin

addressbus<=addressbus+1;

we<=0;

CAPING<=0;

if(!IGPV)begin

state<=idle;

CPING<=0;

end

else state<=startcaping;

end

default :state<=idle;

endcase

end

endmodule

`timescale 10ns/1ns

module capcard (we,

nrd,

addressbus,

reset,

CS_V1,

CAPING,

CAPSTR,

ICLK,

IDQ,

IGPV,

IGPH

);

input CS_V1,CAPSTR,ICLK,IDQ,IGPH,IGPV,nrd,reset;

output CAPING,we;

output [17:0] addressbus;

wire IGPV,nrd,CS_V1;

reg we;

reg [17:0] addressbus;

regCAPING;

reg [2:0] state;

parameter idle=3'b000,startcapflag=3'b001,//FSM

wait_vstart =3'b010,wait_vend =3'b011,

wait_hstart =3'b100,wait_hend=3'b101,

startcaping=3'b110,read_flag=3'b111;

initial

begin

addressbus<=18'b00_0000_0000_0000_0000;

we<=1;

CAPING<=1;

state<=idle;

end

always @ (posedge ICLK or negedge reset)

begin

if(!reset)begin

we<=1;

CAPING<=1;

state<=idle;

end

else

case(state)

idle:

if(!CAPSTR)

state<=startcapflag;

else if(!nrd)

state<=read_flag;

read_flag:begin

addressbus<=addressbus+1;

CAPING<=1;

end

startcapflag:

if(!IGPV)begin

state<=wait_vstart;

end

wait_vstart:

if(IGPV)begin

state<=wait_vend;

end

wait_vend:

if(!IGPH)begin

state<=wait_hstart;

end

wait_hstart:

if(IGPH)begin

state<=wait_hend;

end

wait_hend:

if(IDQ)begin

state<=startcaping;

end

startcaping:begin

addressbus<=addressbus+1;

we<=0;

CAPING<=0;

if(!IGPV)begin

state<=idle;

CPING<=0;

end

else state<=startcaping;

end

default :state<=idle;

endcase

end

endmodule

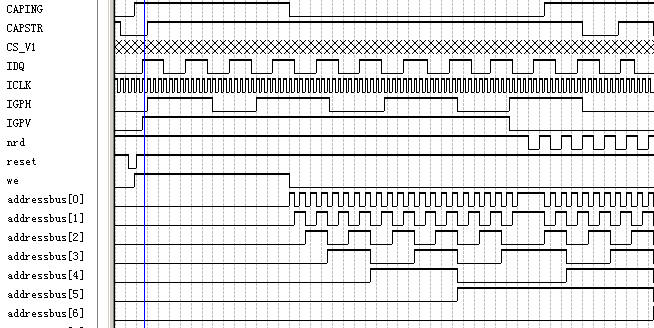

timing仿真

function仿真

另外为什么系统提示: 您所在的用户组无法下载或查看附件啊?我自己写的帖子怎么都看不到图片呢?

下岗待业的是看不到附件的,多赚点钱吧。

看了一下

有点建议:

1。你把用来状态转换的always和其他的几个变量赋值分开写,这样清楚许多,

感觉we, CPIN可以用state的组合逻辑实现

2。addressbus这个信号没有被reset初始化,有可能有问题。

我觉得是reset给的不对,开始的时候reset为1,初始化的状态怎么给定呢,你的FSM的开始运行应该是在reset由0变1之后,CAPSTR在reset回到1之后就一直为1,FSM应该一直处于Idle状态,你看看你的state那根bus看看状态怎么进行转移的,个人意见不知道对不对,请大家指点。

还有就是,FSM还是写成两个always的好理解也好维护一些

可综合代码里是不能有initial的