模块和仿真模块在仿真时的波形区别。

[求助]模块和仿真模块在仿真时的波形区别。

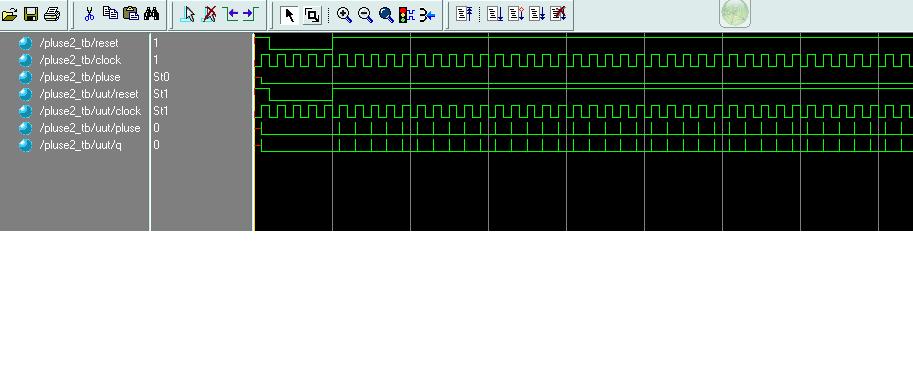

就是图上的pluse2_tb/pluse和pluse2_tb/uut/pluse为什么不同呀!

这个是模块pluse

always @(q)

pluse=q;

always @(posedge pluse or posedge clock)

if(reset==1'b0)

q=0;

else

if(pluse==1'b1)

q=0;

else

q=1;

这个是测试模块pluse_tb

pluse2 uut (

.pluse(pluse),

.reset(reset),

.clock(clock)

);

// Initialize Inputs

initial begin

reset = 1;

clock = 0;

end

always

#5 clock=~clock;

initial

begin

#10 reset<=0;

#40 reset<=1;

#400 $stop;

end

[求助]模块和仿真模块在仿真时的波形区别。

有人知道吗?真的不明白是什么意思,很迷惑了

[求助]模块和仿真模块在仿真时的波形区别。

基本概念了。

一个是你的rtl设计

一个是对这个rtl 模块的仿真模块,

[求助]模块和仿真模块在仿真时的波形区别。

是不是意思是说我的思路对的,但是在任何硬件上都不可以实现?

但是我觉得利用硬件的延时来产生这样一个脉冲信号,应该是可以的呀!

即使在布线后,加入了硬件的延时,仿真后也是这个样子。

是不是这种思路在verilog里是不正确的?

[求助]模块和仿真模块在仿真时的波形区别。

你这样得到的脉冲信号不受你控制,其实就是毛刺。

另外,你的两个pulse[对不起,你是pluse]信号波形不一致是由于你的module pluse2的verilog语法问题造成的,在always @(posedge pluse or posedge clock)中对q的赋值应该用非阻塞'<='而不是'=',这样它才会一致。

[求助]模块和仿真模块在仿真时的波形区别。

呵呵,英文有点小差。:(

我就是想得到一个和时钟相同的的脉冲,这样如果再用时钟的另一个延触发得到另一个脉冲,就能达到一个倍频的效果了:)只是一个思路:)

谢谢楼上的指点,刚开始学习,问题很多,再论坛上得到很多指点,谢谢大家

[求助]模块和仿真模块在仿真时的波形区别。

改成<=就好了:) 但是综合后的电路是一样的,后仿的时候依然没有脉冲的产生:(

是不是思路的问题呀!