做了个滤波电路总自激,怎么回事?

时间:12-13

整理:3721RD

点击:

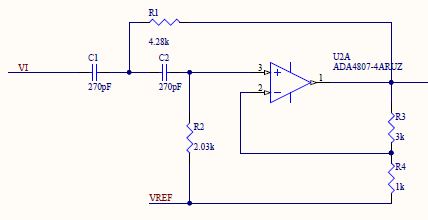

做个了sallen key结构的高通滤波器,参数如图所示,运放电源3.3V,vref是电源电压的一半,测试时,输入接个电阻到地,大于1K时,会出现自激,输出有120KHz左右的方波,感觉是不是电路架构有问题?

用adi网站上的滤波器设计工具设计的结构,用multisim仿真通过了,才做的板子,结果一堆问题,这只是第一个。

低通滤波电路:

用adi网站上的滤波器设计工具设计的结构,用multisim仿真通过了,才做的板子,结果一堆问题,这只是第一个。

低通滤波电路:

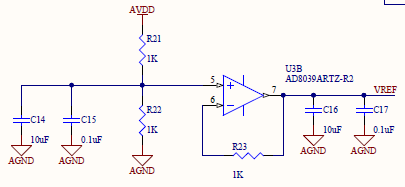

Vref生成电路:

你用的什么运放啊

ADA4807-4 四运放,两个高通然后两个低通

参考电压产生是用AD8039

图上标着

你就直接照他的型号用了?真有钱!

也不是,型号是后来自己选的

低噪声、轨到轨、一定的带宽、4运放,体积要小,就没几个了

结果板子出来了,信号还没有,各种噪声一大堆,现在一级一级排查

180M。。。这带宽也太大了

你需要多大啊

re

REF电路是ADI的Filter Wizard工具给的,如图

用pspice完整的仿真一遍

信号很小,可能要放大数百倍,所以选了个增益带宽积大的,可以灵活分配各级的放大倍数

但是自激的是120KHz左右的方波,频率并不高,不会是它的带宽大的问题吧

确实发现过,这个Vref电路直接振荡了,摘掉这两个电容就好了

不过这个板子的Vref没振荡,所以没注意

后天再核实一下,看看这个板子这两个电容焊没有

但是感觉不是这里的问题

会不会是Vref接入点的问题,R4是不是可以接地?

看了下午的记录,Vref现在很干净,示波器10mV档看不到噪声

filter solution是把运放当理想的,而实际运放并不是理想的

如果运放有模型,带进去仿真一下

analog不需要调试,一切现象都可以在设计阶段仿真出来

最后一句无法赞同。

仿真很必要,也能解决一些基本问题。但是调试必不可少。

正反馈比负反馈大了。你可以尝试 减小负反馈电阻,或者增大正反馈电阻。

增大r1 减小r3

仿一下ROC,看alpha和beita的夹角直接判断,正反馈和负反馈分别仿