请教一个运放影响信号源的问题

时间:12-13

整理:3721RD

点击:

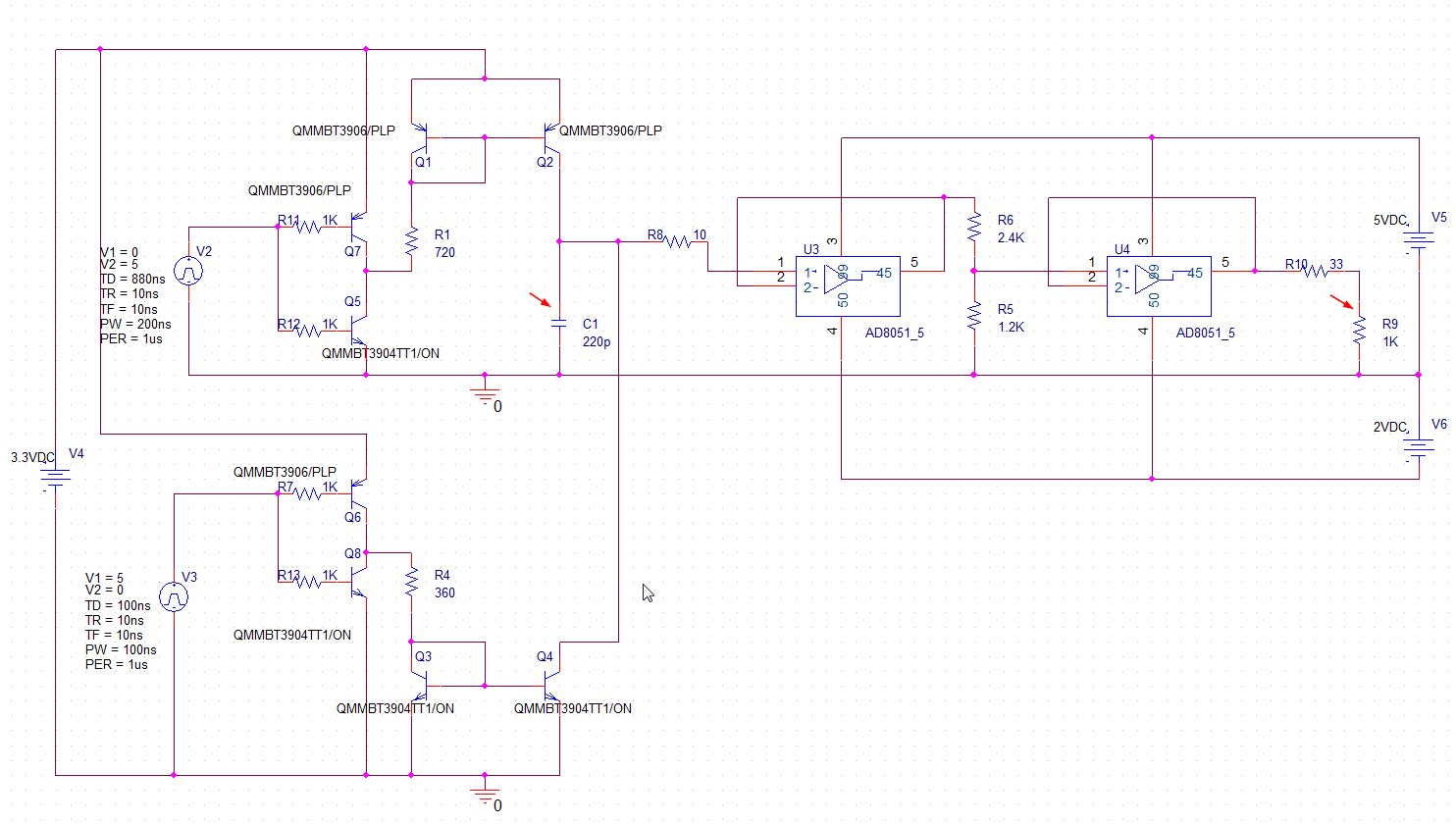

这个电路的用途是产生一系列三角波,上升/下降沿宽度一两百纳秒,脉冲之间的间隔

几百微秒,摆幅1V,大概原理就是用三极管搭两个恒流源,给一个小电容充放电,产生

一个3.3V高的三角波,再用运放缩小一下,变成1V高的。

经过本版网友帮忙,终于PSPICE仿真成功,现在开始搭实际电路,仿真时的脉冲源和

推挽电路(V2、V3、Q5~Q8)用FPGA的I/O代替,发现电路只有前半部分时工作很好,

即在C1处测量有三角波信号,但是再加上运放部分后,电容C1处的波形变形了。

理想波形如图中红色曲线,实际波形如图中手画的橙色曲线。我怀疑是运放的输入在

向电容C1充电,因为实际电路中两个脉冲的间隔比仿真大得多,达到几百微秒,所以

C1上的电会被充起来。这里用的运放AD8052的输入偏置电流为3.25uA,好像很大?

有什么办法呢?换个偏置电流小的运放?改电路?我现在的模电几乎全忘光了,

附上电路图和仿真的波形,大家帮忙看一下。

几百微秒,摆幅1V,大概原理就是用三极管搭两个恒流源,给一个小电容充放电,产生

一个3.3V高的三角波,再用运放缩小一下,变成1V高的。

经过本版网友帮忙,终于PSPICE仿真成功,现在开始搭实际电路,仿真时的脉冲源和

推挽电路(V2、V3、Q5~Q8)用FPGA的I/O代替,发现电路只有前半部分时工作很好,

即在C1处测量有三角波信号,但是再加上运放部分后,电容C1处的波形变形了。

理想波形如图中红色曲线,实际波形如图中手画的橙色曲线。我怀疑是运放的输入在

向电容C1充电,因为实际电路中两个脉冲的间隔比仿真大得多,达到几百微秒,所以

C1上的电会被充起来。这里用的运放AD8052的输入偏置电流为3.25uA,好像很大?

有什么办法呢?换个偏置电流小的运放?改电路?我现在的模电几乎全忘光了,

附上电路图和仿真的波形,大家帮忙看一下。

你Q5~Q8画反了吧,集电极和发射极应该倒过来。

AD8051/2的输入阻抗太小了,只有290k,换个JFET工艺的运放试试呢,比如AD8065/6,输入阻抗是1000G。。。偏置电流是pA级

我检查了一下,应该是没错把,反了的话仿真结果也不会正确的

好的,我试试,谢谢 :-)

看你的设计思路,推挽是共集电组态,同相输出, 你的图里是共射组态,反相输出,看着是一个开关。另外三极管的C、E颠倒一下,有的电路也是可以工作的,但性能差很多。

嗯,那两对推挽确实工作在开关状态。和Vpulse一起模拟FPGA的输出。

周期是300ns的电流源给电容充电?我觉得你应该先用电阻代替C1,看看方波是否正常工作,如果方波能正常工作,那可能就类似于积分饱和的现象,但运放的偏置远小于你电流源的电流,输出应该是慢慢上去而不应该一个周期就上去了,试试在C1两端并一个电阻,但是别太大也别太小。

嗯,有道理,先试试方波。输出确实是慢慢上去的,仿真过程中为了

多看几个周期,脉冲的频率很高,脉冲之间的间隔只有几微秒,实际

电路中脉冲的间隔是几百微秒。

脉冲间隔1微秒和100微秒差别很大的,1微妙基本不用考虑运放偏置电流的影响,100微妙就必须考虑了。