如何在PCB上给多路RF transceiver提供完全同步的本振信号

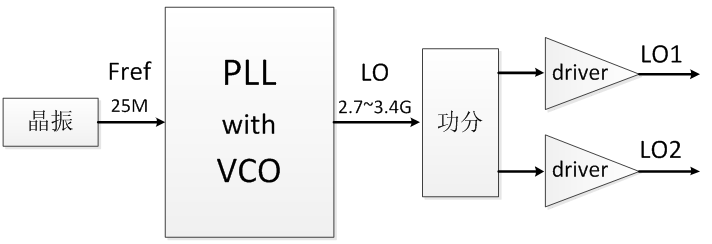

但是由于所需本振频率较高(2.7~3.4G),找不到这样的功分器,所以想了另外两种方案:

第一种,直接用PCB上的走线将PLL的一路输出变为两路,再加LO driver:

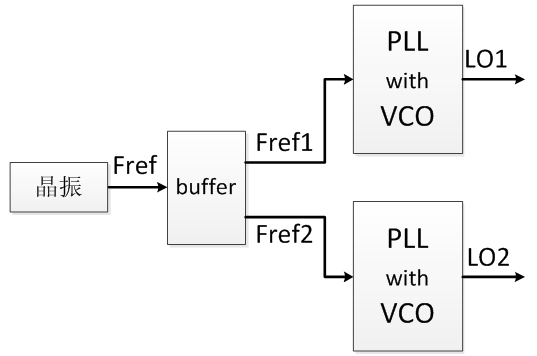

第二种,用一个晶振通过一个两输出的buffer给两个PLL提供参考输入,这样来产生两路本振信号:

请教一下上面两种方案哪种好点,或是有什么更好的方案吗?多谢了。

方案2没有办法保证完全同步。

方案1做好阻抗匹配工作可行。

方案2可行性高,前提是要找到精度、相噪参数达标的时钟,时钟BUFFER一般都能达到延时小于3ns的指标,同一片buffer俩路输出的时延参数一致性应该没问题。所以PLL倍频后的本振信号也没问题。

方案1分俩路后,VCO带负载的能力要够,而且要保证俩路的负载是一致的。这种情况下方案1才能满足需求。

方案一相当于自己用微带线设计一个功分器呀

今天问了PCB厂家,这样直接把微带线分叉无法保证都是50欧的阻抗,只有找功分器了

怎么和一楼说的相反啊...

感觉方案2两个PLL的锁定时间可能不确定,

方案1在VCO输出那里加一个很强的LO driver可以解决VCO的带负载能力吗

就是不会用微带线做功分器,所以就只能直接把它分成两根线了...

pcb厂家这么弱?微带线分叉,然后串0 ohm电阻来调整阻抗吧。

找到了一个可以产生四路输出的PLL(集成VCO),TI的TRF3765,datasheet里说了“Outputs are phase-locked but not phase-matched”,是不是就意味着无法保证这四路输出相位同步了...

嗯。为啥一定要相位同步?

我也想问这个问题,lz在后面校准和补偿一下不行吗?

还能校准和补偿?这个难度更高吧?

不是rf tranceiver吗,我觉得在基带可以补,这种相位差的效果应该跟IQmismatch差不多,没仔细想

给802.11ac做的四发四收的RF transceiver,接受的四路信号是同步的,要求发送的四路信号也同步,所以我感觉给它们的四路本振信号也应该要同步才行。

接受的信号是一个源吗?否则,如何保证是同步的?

本振信号是同步的,并不能保证发送也是同步的吧。

所以还是要明确下 同步 的含义。

接收的四路怎么保证同步的?