PLL求助

调试一PLL,adf4157鉴相芯片,10MHz参考,环路大概100khz左右

要求锁定时间比较短,一般30us吧。

例如 让他中心频率5.99GHz, 扫宽1Hz ,扫描1万多个点,平均80us一个点。

每次都会些adf4157,即使频率是mHz级别的改变,

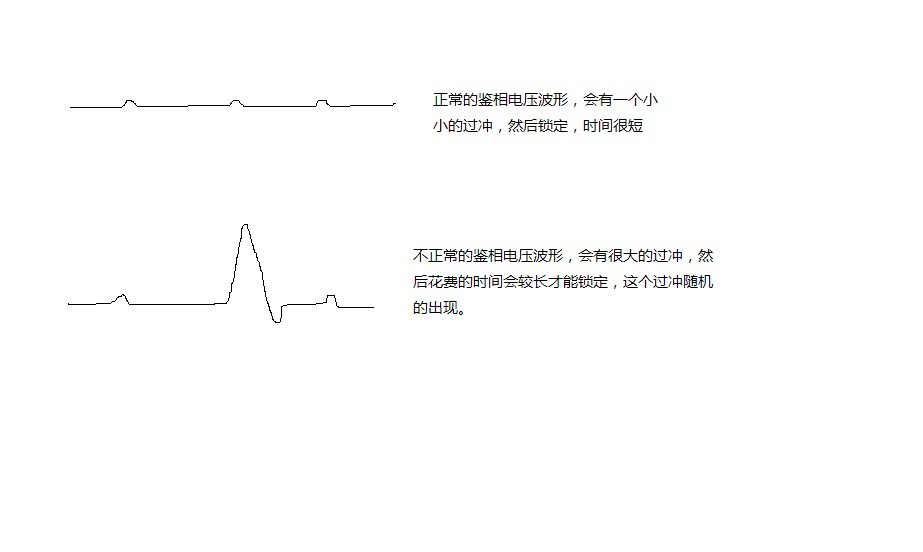

用示波器交流检测鉴相电压,可以看出大部分的频率切换点会稍微上升一点,然后就锁定。

但是随机的会出现突然的一个很大的过冲,然后在锁定。

如图所示的

在上面表示出波形出来,因为调谐得比较小,而且很大的过冲出现是随机的,虽然能锁定,但是时间比较长,导致采样的时候会出现误差。

想问下论坛里面的高手,这个问题是怎么出现的? 是硬件设计有问题吗?(个人不知道该怎么分析,如果说是硬件的问题,但是这个是随机出现的,除非说是在临界状态,但是改变环路啥的,貌似都有这种情况。

也做了其他的实验,换频率点,比如说4GHz的位置,貌似就不出现了,4G和5.99G的那个Kv貌似差别有点大,4G大概在150-200MHz/V ,5.99G大概在50-80MHz/V ,不过我改变电荷泵的电流貌似也没有改善)

所以想请坛里面的PLL高手指点下。

--

确定增大电荷泵电流没有效果吗?电荷泵电流变化了多大范围?

在 fiyan 的大作中提到: 】

: 调试一PLL,adf4157鉴相芯片,10MHz参考,环路大概100khz左右

: 要求锁定时间比较短,一般30us吧。

: 例如 让他中心频率5.99GHz, 扫宽1Hz ,扫描1万多个点,平均80us一个点。

: ...................

恩,应该没有效果的,限流电阻是5.11K

电荷泵的控制字我差不多是从最低的0000 一直到1111

因为是用示波器捕捉,总是会有上升很大的过冲,貌似出现的概率没有明显改善,所以我认为作用不大

因为是3-6G的VCO,尽量保持一致性,所以不太想分段用不同得环路滤波器。

不过呢,觉得这个不是环路的问题,毕竟是随机出现的过冲。

你说的随机出现,是指切换频率控制字重新锁定的过程出现大过冲

还是说锁定以后就会随机出现这样的现象?

切换频率控制字重新锁定的过程出现大过冲.但是不是每次都出现, 只是随机的出现,但是也都锁定得住。

因为我要求在切换频率后4,50us后采样,如果出现大的过冲的话,锁定时间长,采样的时候环路没有真正的锁定。

但是如果不出现大过冲,锁定在30us之内,采样的时候就是锁定的状态,就不会有问题

现在就是这个比较大的过冲是随机出现的,不知道是什么造成。

如果锁定后出现的话,那稳定是没有锁定。

我们以前遇到过一个类似的问题,不知道你有没有

原因是频率控制字load的时候有毛刺之类的,或者和分频器没有同步上

导致分频比先在一个很错误的比例上分了一拍,然后PLL就有点儿失锁,后来分频比都采对了,就又重新锁定纠回来了

哦,但是我这个是10MHz的鉴相信号,直接进入ADF4157的,当时也考虑会不会鉴相的时候出现最差的情况,造成的大的过冲。

发送频率字得状态机的时钟用的是鉴相信号,分频器也是内部ADF4157产生的

想问下,你们是怎么改善分频比和解决这个load控制字的毛刺的呢?

我们用状态机的模式发送数据的,应该很少会出现毛刺

感觉如果是这种情况的话,就是不同步造成的?

谢谢了

我不清楚ADF4157里面是怎么做的,一般频率控制字会用同参考时钟同频但是不同相的时钟load到分频器去,也可能正好采到你控制字的变化沿上了

建议你们简单把频率控制字前后调一下延时看看有没有改善

如果真是这种同步问题,改一点儿延时应该有巨大的改善或者恶化

恩,好的,谢谢,明天的时候去试一试。

不过4G的时候就没有出现,但是也得死马当活马医。

问题查到了,是adf控制字有个地方没设置好

他的rd reset 我设置成0的。

想着每写一次数据,小数分频功能就复位一次,这么考虑的目的就是防止到时候切换频率,怕频率之间误差大,会有大的跳动。

但是事实相反,要防止切换频率时频差大,就不能复位小数分频功能。

呵呵,南辕北辙了

不过谢谢你~

给了思路。