各位模拟大牛帮我分析下,为什么电平被抬上去了

时间:12-12

整理:3721RD

点击:

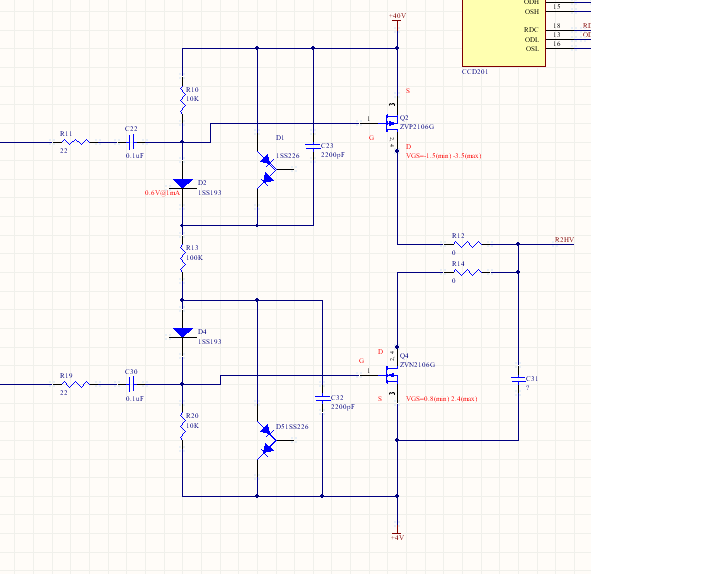

想要电路实现的功能是: 输入0-5V 5MHz方波,占空比 2:1,输出同样形状的方波,高电平40V,低电平+4V, 输入的方波从 R11和 R19 的左端同时输入,输入高电平时,下面的管子Q4导通,输出+4V; 输入低电平时,上面的管子Q2导通,输出+40V,我现在的问题是: 输出+40v没问题,但是输出的低(+4V)却变成了+12V, 我的+4V是从一个LDO输出的,现在发现这个电平被抬高了,电源没有连到电路的时候是+4V,连 到电路上就变成了+12V,我猜应该是电路设计的问题,但分析不出来具体哪有问题,谢谢了

把bmp改成png再贴吧,这么大怎么看

ldo 没办法 放电,它只能在输出比它设定低的时候起作用。

简单说,一个1.2伏的ldo,如果你把输出拉到1.5v,ldo是没办法把它拉回来的。

你可以简单验证一下,把+4伏换成GND,如果输出逻辑对,那么应该就是ldo的问题。你需要一个能吸负电流的DCDC。

有没有其他办法,改善下电路,LDO 不变

电路设计的不好,靠电阻分压来实现4v输出,自然要受制于外电路的负载了

4V 使用LDO提供的,也试过电源直接供给,不是用电阻分压

你先看看两个栅极上的波形,确定该导通的时候完全导通了。

另外输出后面加的什么负载?可能是容性负载,电没放完,可以试试加个阻性负载,就有放电的回路的。

P管和N管导通没问题, 我后面加了电阻试了,好像就像 convter 说的,+4V LDO电源 没法sink current

我现在到处找这类电路,如果是40V-0V 没问题,但40V-4V 就不行,+4V总被抬上去

那你可以这样试试,加一个4点几v的稳压管上去,就可以了,不知道市面上有没有4v多的稳压管。。

频率高且变压摆幅大的电路会受到负载大小极大的限制,尤其是容性负载

你这问题跟前面帖子的PWM电路输出有高频噪声一个问题

在一个成百上千uf级别的电容上,能出现一个摆幅2V的30MHz的信号?那得多牛掰的驱动才行啊

2V 1000uF的话, 充满电荷是Q=UC=2e-3C

30MHz的话,周期是33ns,要在半个周期充到2e-3C, 那么I=Q/t=60kA

不用想了。。。