cadence spectre 运放设计 瞬态仿真

时间:10-02

整理:3721RD

点击:

各位大神 ,麻烦各位 帮我看看 这两幅图是如何得到这样的结论的?

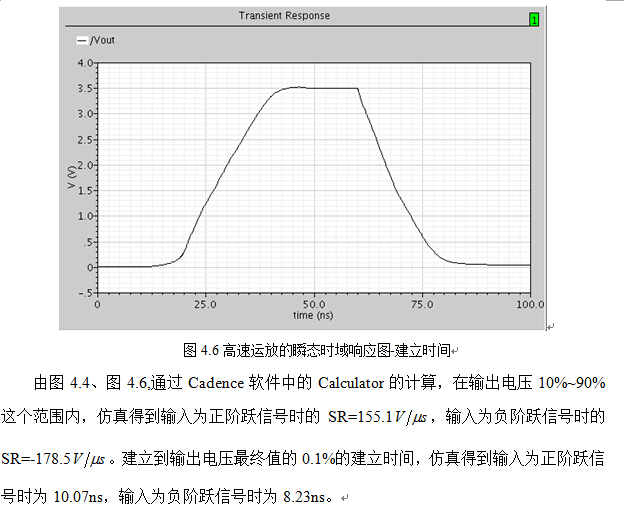

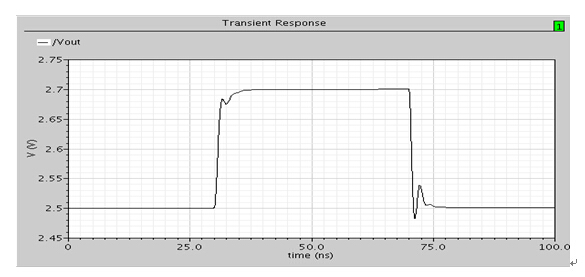

各位大神 ,麻烦各位 帮我看看 这两幅图是如何得到这样的结论的?由图4.4、图4.6,通过Cadence软件中的Calculator的计算,在输出电压10%~90%这个范围内,仿真得到输入为正阶跃信号时的SR=155.1 ,输入为负阶跃信号时的SR=-178.5 。建立到输出电压最终值的0.1%的建立时间,仿真得到输入为正阶跃信号时为10.07ns,输入为负阶跃信号时为8.23ns。

先看书把运放的参数指标含义理解了。这些都是很基础的东西。

Actually I didn't get the problem as the post is not fully descriptive, do you mind re-post it with much more details?

Thanks,

- Muhammad

谢谢小编分享资料 收下了

这里信元扣得的很快啊,瞬间减少

的咚咚咚咚咚咚咚咚咚咚咚咚