高阈值低压降的电流源设计

时间:10-02

整理:3721RD

点击:

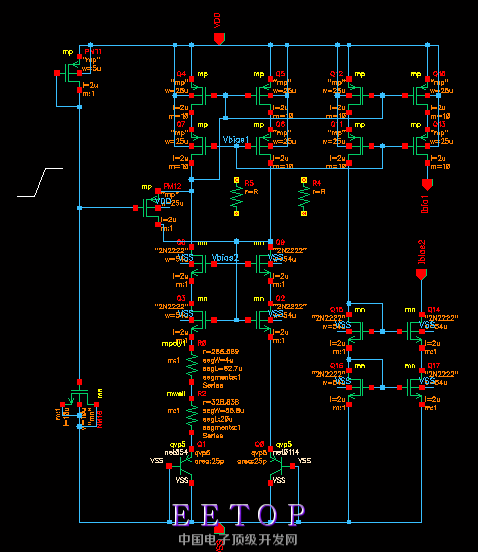

求大神指导高压电路中恒流源的设计(精度误差0.2%),采用浮动地VS,VDD与VS压差为5±0.1V,高压N/PMOS的Vth>1.5。以下为双层结构:

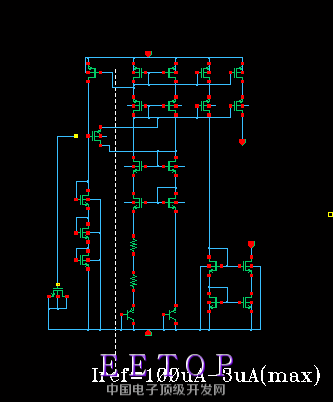

方法一:如图所示,普通低压管VDD电压>5V,高压管至少大于8V

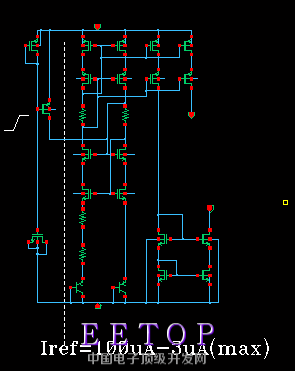

方法二:将电阻插入作self-bias,对于普通低压管4.3V(电流100uA,低电流下VDD还可以更低一点)左右就可以正常工作

如果采用单层,输出精度又特别差,我想了一下如果将第二种结构的第二层VG使用额外的偏置电压,我又该怎样设计呢?

除了这些,是否可以对单层结构采用运放呢?或者还有其它比较好的方法,望大流们指导指导。