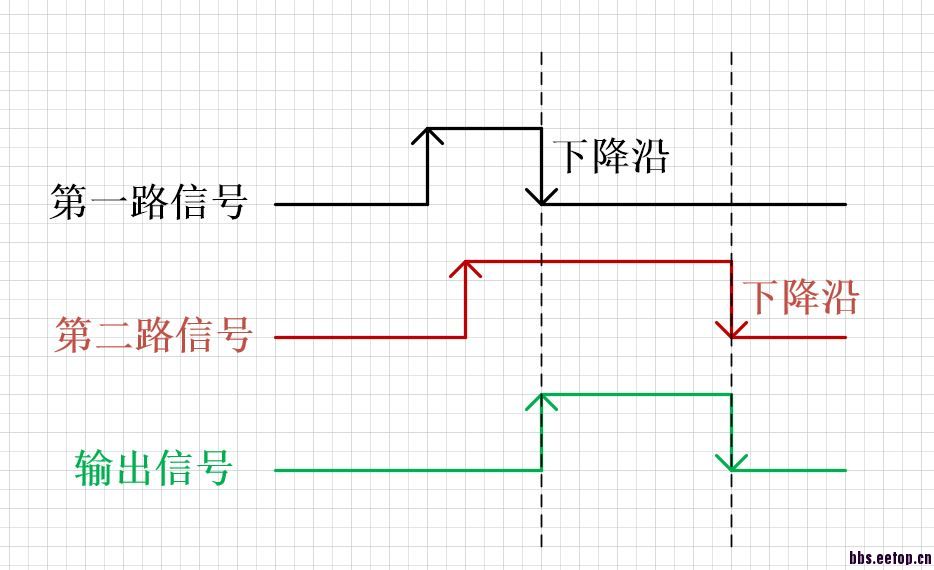

请教大神们,下降沿触发的逻辑电路该怎么实现?

用JK or D FFT

reg reg_a, reg_b;

wire reg_rst;

always @ ( negedge s_a or posedge reg_rst )

if ( ~ reg_rst )

reg_a <= 0;

else

reg_a <= 1;

always @ ( negedge s_b or posedge reg_rst )

if ( ~reg_rst )

reg_b <= 0;

else

reg_b <= 1;

assign reg_rst = reg_a & reg_b;

assign out = reg_a & ~ reg_b;

额,我是想用元器件怎么搭,不是逻辑代码。

那上面不就是电路么?两个触发器,两个与门啊。

只是不是图片方式描述的。

very good

好的,多谢,我好好研究一下大神的代码。

要是通过这种方式实现了我的功能,就给大神你报喜!

这个不是什么高深的逻辑,是最常见的鉴相器代码。lz可能是不熟悉吧。

额,不是数电出生,没怎么搞过触发器。上来就是直接学FPGA了,用触发器搭电路确实水平不行。

写verilog的时候也要在脑内能够大概推测自己写出来的代码会综合成什么样的电路的

撕下来感觉咋样?农用吗?