从事模拟设计多年的人,求助一个数字初级问题。

从事模拟设计多年的人,求助一个数字初级问题。

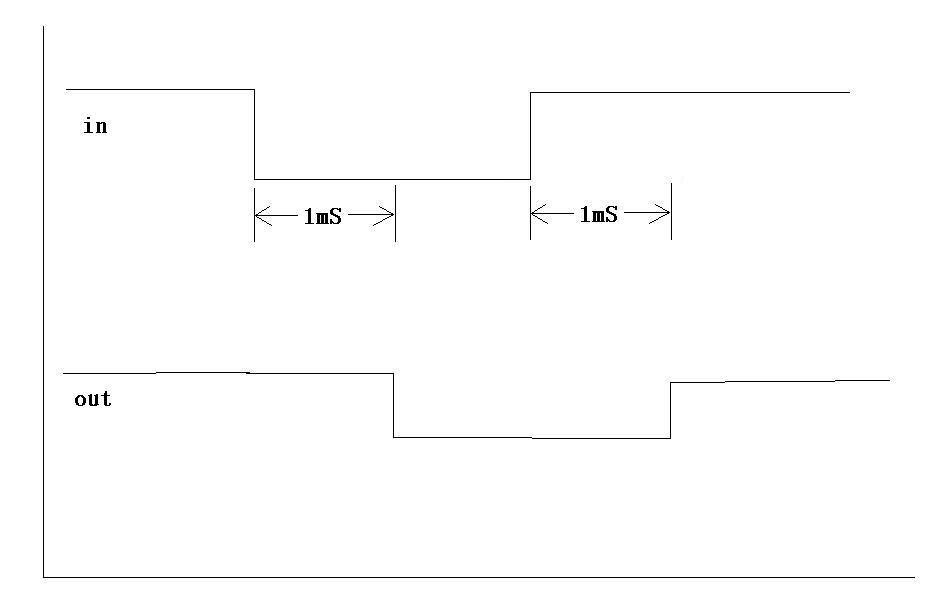

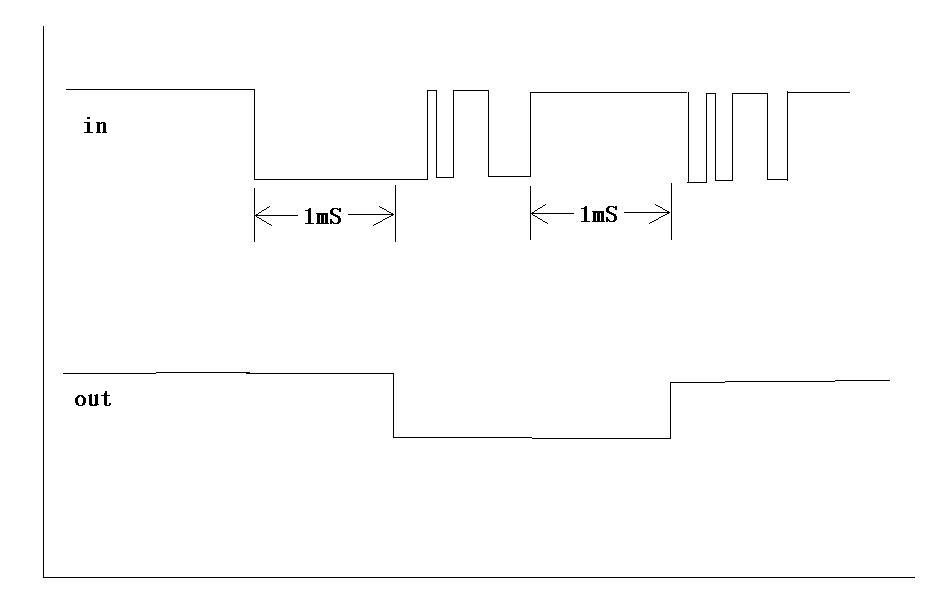

希望实现的功能如图,同时有32K的时钟。

其实很简单,就是输入持续为低1mS,输出就为低。输入持续为高1mS,输出就为高。

1ms不用太精确 0.8~1.2mS以内都行,不要太复杂,不用考虑太特殊的情况。比如1mS内输入一直为低,就是中间有几个微秒的时间短暂为高,短暂的高电平可以忽略。

你能否给我门级的电路图。能否发到 ictuijian@163.com 谢谢啊。

没人,可怜啊

这个用555定时器不能做吗?555+简单的逻辑应该可以的

你这个问题看起来很简单,但实际不好搞。

主要原因就是怎么忽落中间不规则信号。如果是规则的直接降频就可以,但是从你的要求看不是。

所以我的建议还是用模拟方式吧,加个二级滤波就可以解决。

能否加个检测脚,在多少时间内检测到的信号是同一个信号,则确认输入改变,然后输出改变

这个类似于一个信号的发生,简单点的办法,用一个单片机可以解决的,但是小编如果想用硬件去实现,还是有点困难的, 看能不能用比较器去实现你说的这个波形。 个人感觉窗口或者滞回比较器可能有点思路。

两个施密特反相器中间加一个RC1ms延迟不知道是否可以。

这个感觉有点思路阿, 利用rc延迟和施密特的阈值电压来滤除抖动. 可问题是RC电路不是模拟的吗?那这是模数混合了。

这个用HDL比较好做,对信号用时钟采样,根据时钟的频率,连续N个1或者0才输出1或者0.

我有个问题,如果输入信号既不满足高电平持续1mS或以上, 也不满足低电平持续1mS或以上,那输出应该是什么状态呢?

我写了一段Verilog的代码,可以实现你说的功能:

因为你是32KHz的时钟,所以当脉冲宽度小于1/32kHz时,有可能采样不到!

`define time_1ms 32 //32KHz system clock

module signal_process( clk, rst, din, dout );

input clk;

input rst;

input din;

output dout;

reg dout;

reg [1:0] state;

reg [5:0] cnt_high;

reg [5:0] cnt_low;

//*******************************************************************************************

//state transfer: input(state and din), output(state)

//*******************************************************************************************

always @( posedge clk )

if(rst) begin

state <= 2'd0;

cnt_high <= 6'd0;

cnt_low <= 6'd0;

end

else begin

case(state)

2'd0: begin

if(din) begin

cnt_low <= 6'd0;

if(cnt_high == `time_1ms) begin

cnt_high <= 6'd0;

state <= 2'd1;

end

else

cnt_high <= cnt_high + 1'b1;

end

else begin

cnt_high <= 6'd0;

if(cnt_low == `time_1ms) begin

cnt_low <= 6'd0;

state <= 2'd2;

end

else

cnt_low <= cnt_low + 1'b1;

end

end

2'd1: begin

if(!din) begin

cnt_high <= 6'd0;

if(cnt_low == `time_1ms) begin

cnt_low <= 6'd0;

state <= 2'd2;

end

else

cnt_low <= cnt_low + 1'b1;

end

else begin

cnt_low <= 6'd0;

end

end

2'd2: begin

if(din) begin

cnt_low <= 6'd0;

if(cnt_high == `time_1ms) begin

cnt_high <= 6'd0;

state <= 2'd1;

end

else

cnt_high <= cnt_high + 1'b1;

end

else begin

cnt_high <= 6'd0;

end

end

default: ;

endcase

end

//*******************************************************************************************

//give a value to dout according to state

//*******************************************************************************************

always @( posedge clk )

if(rst)

dout <= 1'b0;

else

case(state)

2'd0: dout <= 1'b0;

2'd1: dout <= 1'b1;

2'd2: dout <= 1'b0;

default: ;

endcase

endmodule

另外,就是当既检测不到高电平超过1MS,也检测不到低电平超过1ms时,默认输出为0

你自己摆一个gate级的电路应该不难吧,用counter去数就行,input的边沿作为counter的reset信号

感谢诸位的回答,非常感谢

用32k时钟和RS触发器做一个计数器,计数器在in信号变化和计数满1ms时reset,同时计数满1ms时输出out信号。

很好的资料

用32KHz的时钟对输入信号进行采样,使用两个计数器,一个计数器重复计数0-31,另外一个计数器为采样到的高电平个数,每32个时钟周期将计数个数存储,使用组合逻辑进行判断,由于信号有干扰,因此可以定收到高电平个数在25-32个时输出1,高电平个数在0-5输出为低,其余情况可以自定义,用verilog语言很好写的

杀鸡焉用牛刀?最简单的,加二级滤波吧。

路过~

过来看看 都忘光了

滞回比较器应该可以