数模混合求助

时间:10-02

整理:3721RD

点击:

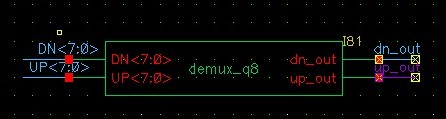

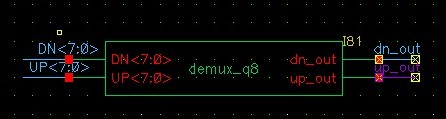

小弟最近在用cadence做数模混合,前面是模拟部分,输出为DN[7:0],UP[7:0],后面接了一个简单的数字模块demux.目的是比较DN[7:0],UP[7:0]中1的个数,分别输出高低电平.demux的代码如下:module demux(UP,DN,up_out,dn_out);

input [7:0]UP,DN;

output up_out,dn_out;

reg [2:0]iup,idn;

reg up_out,dn_out;

integer i;

always @(UP or DN)

begin

iup=3'b0;

idn=3'b0;

for(i=0;i<8;i=i+1) begin

if(UP==1'b1) begin iup=iup+1'b1; end

else if(DN==1'b1) begin idn=idn+1'b1; end

else begin iup=iup; idn=idn; end

end

if(iup>=idn+3'b010) begin up_out=1'b1; dn_out=1'b0; end

else if(idn>=iup+3'b010) begin up_out=1'b0; dn_out=1'b1; end

else begin up_out=1'b0; dn_out=1'b0; end

end

endmodule

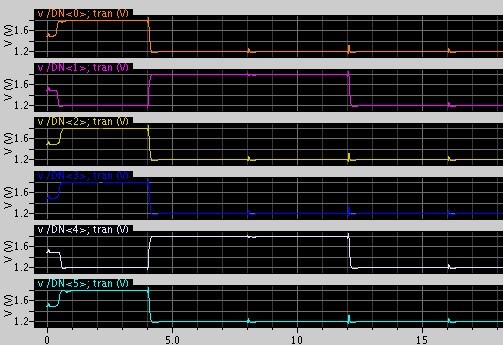

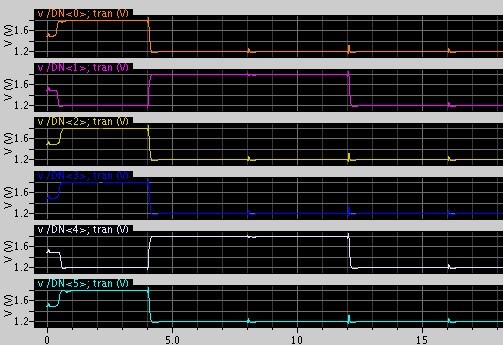

模拟端口输出的结果如图:

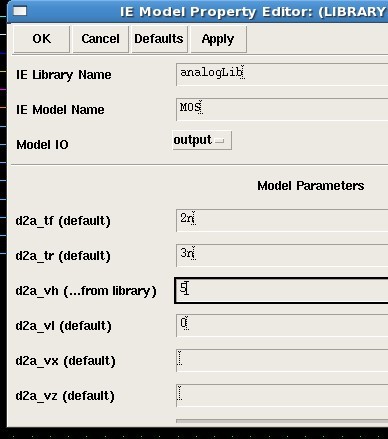

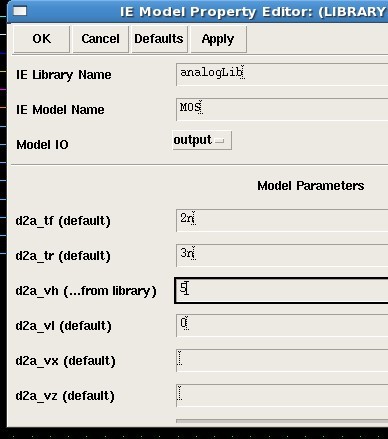

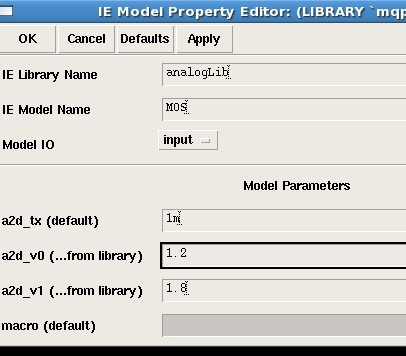

,由于模拟输出最高电平1.8V,最低电平1.2V,所以我的cadence设置如下图所示:

,由于模拟输出最高电平1.8V,最低电平1.2V,所以我的cadence设置如下图所示:

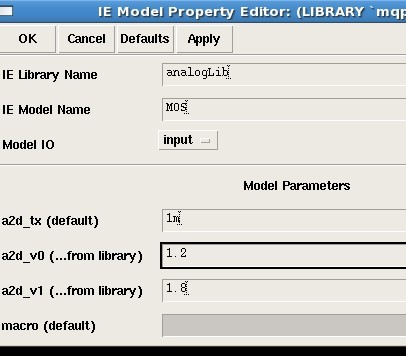

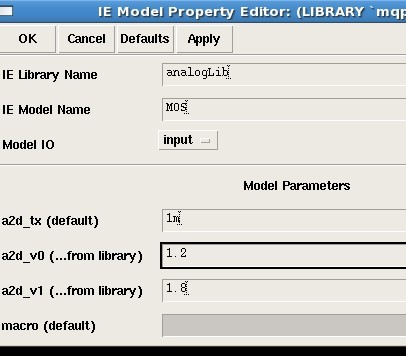

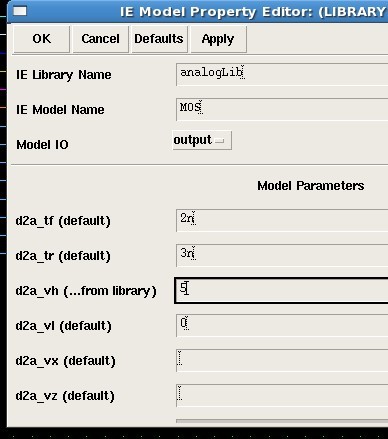

对于cadence的设置如图:

,但仿出来的数字端口dn_out,up_out结果却全为0;理论结果应该是UP_OUT,跟DN_out都要有高电平输出的.请问我的问题出在哪儿呢?请给位大神指点一下小弟,多谢了....

,但仿出来的数字端口dn_out,up_out结果却全为0;理论结果应该是UP_OUT,跟DN_out都要有高电平输出的.请问我的问题出在哪儿呢?请给位大神指点一下小弟,多谢了....

input [7:0]UP,DN;

output up_out,dn_out;

reg [2:0]iup,idn;

reg up_out,dn_out;

integer i;

always @(UP or DN)

begin

iup=3'b0;

idn=3'b0;

for(i=0;i<8;i=i+1) begin

if(UP==1'b1) begin iup=iup+1'b1; end

else if(DN==1'b1) begin idn=idn+1'b1; end

else begin iup=iup; idn=idn; end

end

if(iup>=idn+3'b010) begin up_out=1'b1; dn_out=1'b0; end

else if(idn>=iup+3'b010) begin up_out=1'b0; dn_out=1'b1; end

else begin up_out=1'b0; dn_out=1'b0; end

end

endmodule

模拟端口输出的结果如图:

,由于模拟输出最高电平1.8V,最低电平1.2V,所以我的cadence设置如下图所示:

,由于模拟输出最高电平1.8V,最低电平1.2V,所以我的cadence设置如下图所示:对于cadence的设置如图:

,但仿出来的数字端口dn_out,up_out结果却全为0;理论结果应该是UP_OUT,跟DN_out都要有高电平输出的.请问我的问题出在哪儿呢?请给位大神指点一下小弟,多谢了....

,但仿出来的数字端口dn_out,up_out结果却全为0;理论结果应该是UP_OUT,跟DN_out都要有高电平输出的.请问我的问题出在哪儿呢?请给位大神指点一下小弟,多谢了....

自己顶起来,,我对此问题纠结了一个星期了.之前以为是数字模块编程的问题,所以我先设计了一个简单的加法器adder,想把模拟输出的DN[7:0],DN[7:0]加起来,看是否有输出结果,但结果也一样的,输出全是0;;;;;;现在我看还是不行,真心不知道问题出在哪儿........①我觉得还是设置问题,估计cadence把模拟输出全默认输出为0了.所以加起来的结果也是0.....不知是不是这样...

有哪儿懂这个吗?/请指点一二...............万分感谢....你的仿真过程软件设置是否有问题。我以前用过混仿,仿真结果和实际是符合的。是用的仿真器是什么?

你好,我用的是cadence仿的数模混合.设置跟仿真步骤都是以严格按照流程来的.我在想是不是模拟输出电压最高为1.8v,有点低,模拟器识别不了,全部默认为低电平了.不知是不是这个原因....请问你是不是也用的是cadence仿真的呢?能不能跟我交流一下?谢谢了有没有类似的书籍给分享给大家的?

a2d_v0和a2d_v1设置的不对吧. 试试都设为1.5呢?