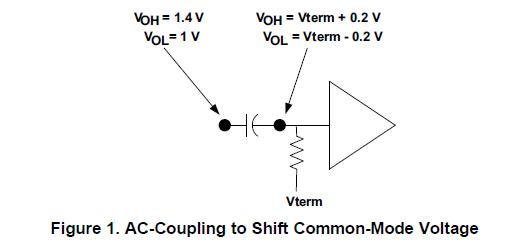

AC耦合的疑惑

我做了一个实验,却发现事实并不像我想的那样

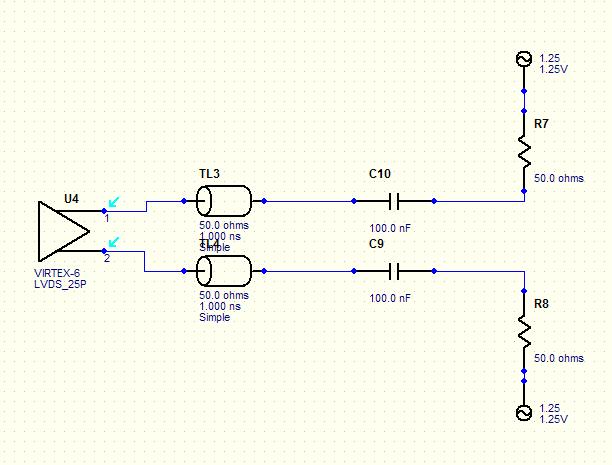

上面是我搭建的仿真模型,驱动器为2.5V LVDS

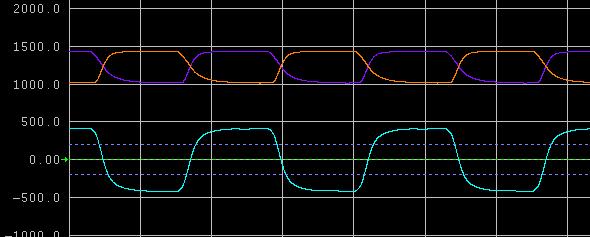

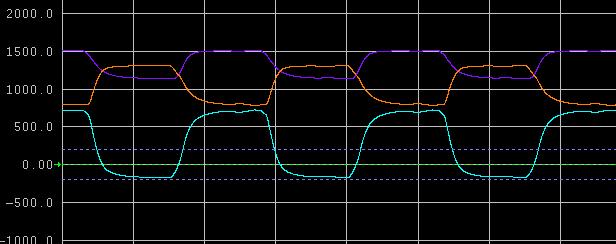

一开始,把耦合电容去掉,直接使用50ohm电阻端接到1.25V(LVDS的偏置电平),得到波形如下,可以看出这个信号质量很好。上半部分为差分电平的两个输出端,都以1.25V为中心上下摆动;下半部分为信号差值,可以看出这个信号是DC平衡的。

加上滤波电容,希望能滤去直流成分,再把信号重新偏置到1.25V,得波形如下。可以看出此波形相比于上面的波形,紫线整体幅度有一定提高,而橙线整体幅度有一定下降,都不是以1.25V为中心(无法理解,差分信号的两个输出端输出的是同样的信号,只有相位差180度,经过的是同样的电路,为什么得到的结果却不一样);而且信号差值也不再是DC平衡的。

再把1.25V上拉电源换为0V,希望能将信号偏置到0V,得波形如下。可以看出几乎和上图一摸一样。我不禁要问,AC耦合有用吗,还是我的仿真本身有问题?

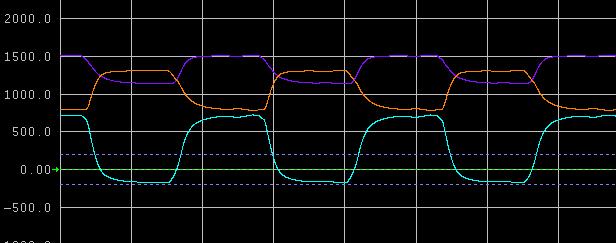

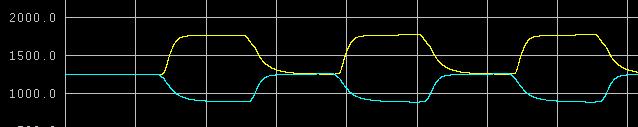

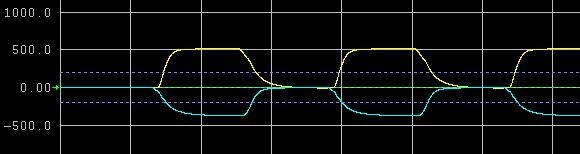

再补两个图,刚才的表述稍有问题,上面的波形图都是信号输出端的波形,并不是AC耦合后的波形,下面两个图是AC耦合后的波形,黄线为R7的波形,绿线为R8的波形

1.25V偏置

0V偏置

可以看出信号都被拉到了一定电平,但是有一根线总是在偏置电平之上,而另一根线线总是在偏置电平之下,并不是以偏置电平为中心上下摆动。这样得到的差分电平总是在0V之上,并非DC平衡。

木有人回复。

你信号的频率是多少? 增大电容看看

信号频率为400MHz,电容从10p到1u都试了,一样的效果。

把频率降到133MHz,电容增大到10u(最大值),结果还是一样

你仿真时间是多久?

试了下100ns,一直都是这个样子

把频率降到1K~1M看看,先验证电容的隔直

如果按照400M的频率来说,100ns 只是仿真了40个周期。我不知道你当时电容挂了多少,你需要算一下RC的常数。怀疑你电容太大,仿真时间又短,从而导致电容能量传递时间不够,没有达到稳态! 减小电容、延长仿真时间看看

频率降到1M,结果还一样

牛啊

说的太对了,我把仿真时间加大到10us,可以看出差分信号逐渐趋于DC平衡了

电容为10nf时,在2.5us处,基本上可以认为是DC平衡了。电容为1nf时,在0.5us之前已经DC平衡了。

如果要计算RC常数的话,假设驱动电阻R为50欧,C为10nf,RC=0.5us,不知道我这样算对不对?

不是太懂RC常数与电容的稳态有什么关系?以前理解RC常数决定了电容滤波的频率,频率高于1/RC的能过去,频率低于1/RC的衰减很大。难道说这个电容先要经过RC时间才能充满电,才能起到滤波的作用?

对这个环路列微分方程,对电容充放电的电压曲线是e^(-t/rc) 的解,可能写的不正确,所以电容上电压要想达到平衡时的时间是和RC有关的

楼上说的真好

目前正在琢磨这个ac耦合的问题呢,很好的参考啊。希望能跟楼上的几位好好讨论下,学习下。

1)接受AC信号的应该是一个完整的电路,你右边的R7,R8电路都不是完整的电路;

2)接收电路要能够承担AC电压的变化,直接接在DC上肯定没有AC信号。

没达到稳态啊

有个问题想请教一下小编,你这个1.25的的电源一直都在会不会干扰信号啊,按道理电容DC建立完毕之后应该关掉1.25V的power的。