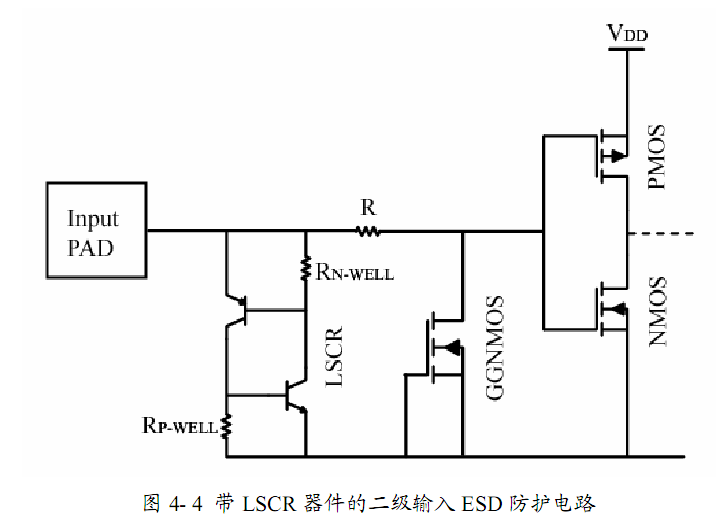

关于ESD GGNMOS溃通问题

请教高人,怎样保证图中的GGNMOS会比NMOS管提前溃通,进行泄电?谢谢!

请教高人,怎样保证图中的GGNMOS会比NMOS管提前溃通,进行泄电?谢谢!

becare of HV stress cause latch-up issue in this system.

此处的ggnmos作为第二级esd保护用,用来保护内部pnmos的gate oxide。为何需要ggnmos要比nmos提早溃通?减小channel length可以获得低的punch through电压,但是esd 的性能比较特殊,建议以foundry提供的esd rule作参考。

这个GGNOMS是用来保护NMOS的吧?如果让GGNMOS先溃通,是GGNMOS的L小于NMOS的L吗?

如之前的回复,这里的ggnmos是用来保护input nmos和pmos的栅氧化层的,只要ggnmos的击穿电压(考虑esd电流)低于栅氧的击穿电压就可。如果没有esd data作支持,不建议自己修改esd device的rule。在input 处,ggnmos的L小于nmos的没有直接的意义。如果是output处,则ggnmos是用来保护输出nmos的,ggnmos的L比nmos的小些是合理的。

谢谢,但怎么保证ggnmos的击穿电压小于栅氧击穿电压呢?

这个一般foundry要保证的,可以看一下所用工艺的pcm spec中oxide和mos的bv值。

谢谢!

一般0.18um的工艺,栅氧的击穿电压会高于junction breakdown voltage,在先进工艺中,比如90nm,65nm也会有3.3V的管子,thick gate oxide, 应该能保证。 如果不能保证这点,就不能采用这种ESD防护方案了

第二级保护,主要保护后面的2个mos管不先被击穿

这个最好结合device的数据来比较才行 做foundry的人不一定意识到这一点的

这个很简单啊,foundry会提供ESD implant这一层,在GGNMOS放入drain端打一层ESD implant,这会使GGNMOS的breakdown 电压低于gate oxide的breakdown电压啊。

在这个GGNMOS加了ESD IMPLANT为什么会使其耐压低于后面的N ,PMOS的?请详解。

我也了解了

认真努力学习 谢谢